# XTX™ conga-XEVAL

Detailed description of the congatec XTX™ evaluation baseboard

User's Guide

Revision 1.3

# **Revision History**

| Revision | Date     | Author | Changes                                                                                                                                                                                                                                                                                                       |

|----------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 17.10.05 | HCH    | Official release                                                                                                                                                                                                                                                                                              |

| 1.1      | 09.11.05 | HCH    | Changed LPT/#FPY Signal; updated debug display description; added TP.                                                                                                                                                                                                                                         |

| 1.2      | 20.01.06 | GDA    | Corrected errors in sections 2.2, 2.4, 3.2.2 and added section 5 "Mechanical Drawing conga-XEVAL". Added link table to connector diagram page. Added description of pins 7 and 8 in the LCD power connector pinout table in section 3.4.2. Changed the LCD Voltage value for Jumper X45 5-6 from 12V to 3.3V. |

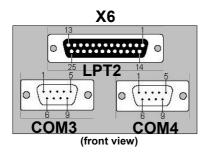

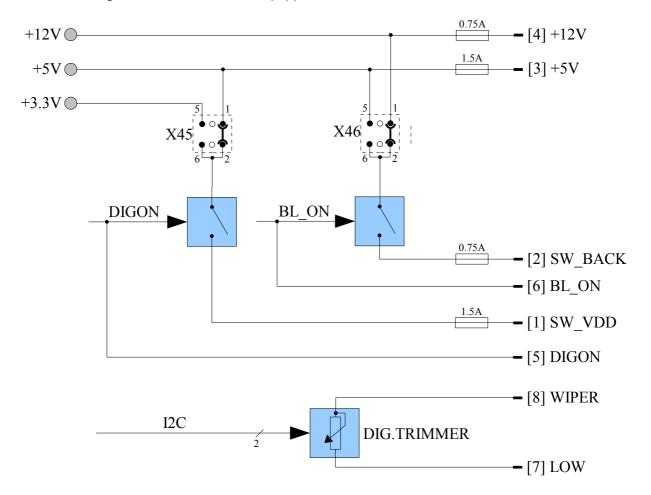

| 1.3      | 20.06.06 | GDA    | Added pinout table for LPT2, COM3 and COM4. Corrected fuse values for X47 pinout, was 15A but the correct value is 1.5A. Added connection possibilities diagram for X47 connector.                                                                                                                            |

# **Preface**

This user's guide provides information about the components, features and connectors available on the XTX Evaluation Baseboard.

#### **Disclaimer**

The information contained within this user's guide, including but not limited to any product specification, is subject to change without notice.

congatec AG provides no warranty with regard to this user's guide or any other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to any of the foregoing. congatec AG assumes no liability for any damages incurred directly or indirectly from any technical or typographical errors or omissions contained herein or for discrepancies between the product and the user's guide. In no event shall congatec AG be liable for any incidental, consequential, special, or exemplary damages, whether based on tort, contract or otherwise, arising out of or in connection with this user's guide or any other information contained herein or the use thereof.

#### **Intended Audience**

This user's guide is intended for technically qualified personnel. It is not intended for general audiences.

# **Symbols**

The following symbols are used in this user's guide:

#### Warning

Warnings indicate conditions that, if not observed, can cause personal injury.

#### Caution

Cautions warn the user about how to prevent damage to hardware or loss of data.

Notes call attention to important information that should be observed.

#### **Connector Type**

Describes the connector that must be used with the XTX Evaluation Baseboard, not the connector found on the XTX Evaluation Baseboard.

#### Link to connector diagram

This link icon is located in the top right corner of each page. It provides a direct link to the connector diagram on page 8 of this document.

### **Terminology**

| Term                 | Description                                                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Express (PCIe)   | Peripheral Component Interface Express – next-generation high speed Serialized I/O bus                                                                                                          |

| PCI Express Lane     | One PCI Express Lane is a set of 4 signals that contains two differential lines for Transmitter and two differential lines for Receiver. Clocking information is embedded into the data stream. |

| x1, x2, x4           | x1 refers to one PCI Express Lane of basic bandwidth; x2 to a collection of two PCI Express Lanes; etc Also referred to as x1, x2 or x4 link.                                                   |

| ExpressCard          | A PCMCIA standard built on the latest USB 2.0 and PCI Express buses.                                                                                                                            |

| USB                  | Universal Serial Bus                                                                                                                                                                            |

| SATA                 | Serial AT Attachment: serial-interface standard for hard disks                                                                                                                                  |

| AC '97 / HDA         | Audio CODEC (Coder-Decoder) / High Definition Audio                                                                                                                                             |

| LPC                  | Low Pin-Count Interface: a low speed interface used for peripheral circuits such as Super I/O controllers, which typically combine legacy-device support into a single IC.                      |

| I <sup>2</sup> C Bus | Inter-Integrated Circuit Bus: is a simple two-wire bus with a software-defined protocol that was developed to provide the communications link between integrated circuits in a system.          |

| SM Bus               | System Management Bus: is a popular derivative of the I <sup>2</sup> C-bus.                                                                                                                     |

| N.C.                 | Not connected                                                                                                                                                                                   |

| N.A.                 | Not available                                                                                                                                                                                   |

| T.B.D.               | To be determined                                                                                                                                                                                |

# **Copyright Notice**

Copyright © 2005, congatec AG. All rights reserved. All text, pictures and graphics are protected by copyrights. No copying is permitted without written permission from congatec AG.

congatec AG has made every attempt to ensure that the information in this document is accurate yet the information contained within is supplied "as-is".

#### **Trademarks**

Intel and Pentium are registered trademarks of Intel Corporation. Expresscard is a registered trademark of Personal Computer Memory Card International Association (PCMCIA). PCI Express is a registered trademark of Peripheral Component Interconnect Special Interest Group (PCI-SIG). I²C is a registered trademark of Philips Corporation. CompactFlash is a registered trademark of CompactFlash Association. STPC is a registered trademark of STMicroelectronics. LynxEM+ is a registered trademark of Silicon Motion inc. Winbond is a registered trademark of Winbond Electronics Corp. AVR is a registered trademark of Atmel Corporation. ETX is a registered trademark of JUMPtec AG. AMICORE8 is a registered trademark of American Megatrends Inc. Microsoft®, Windows®, Windows NT®, Windows CE and Windows XP® are registered trademarks of Microsoft Corporation. VxWorks is a registered trademark of WindRiver. conga, congatec and XTX are registered trademark of congatec AG. All product names and logos are property of their owners.

### Warranty

congatec AG makes no representation, warranty or guaranty, express or implied regarding the products except its standard form of limited warranty ("Limited Warranty"). congatec AG may in its sole discretion modify its Limited Warranty at any time and from time to time.

Beginning on the date of shipment to its direct customer and continuing for the published warranty period, congatec AG represents that the products are new and warrants that each product failing to function properly under normal use, due to a defect in materials or workmanship or due to non conformance to the agreed upon specifications, will be repaired or exchanged, at congatec AG's option and expense.

Customer will obtain a Return Material Authorization ("RMA") number from congatec AG prior to returning the non conforming product freight prepaid. congatec AG will pay for transporting the repaired or exchanged product to the customer.

Repaired, replaced or exchanged product will be warranted for the repair warranty period in effect as of the date the repaired, exchanged or replaced product is shipped by congatec AG, or the remainder of the original warranty, whichever is longer. This Limited Warranty extends to congatec AG's direct customer only and is not assignable or transferable.

Except as set forth in writing in the Limited Warranty, congatec AG makes no performance representations, warranties, or guarantees, either express or implied, oral or written, with respect to the products, including without limitation any implied warranty (a) of merchantability, (b) of fitness for a particular purpose, or (c) arising from course of performance, course of dealing, or usage of trade.

congatec AG shall in no event be liable to the end user for collateral or consequential damages of any kind. congatec AG shall not otherwise be liable for loss, damage or expense directly or indirectly arising from the use of the product or from any other cause. The sole and exclusive remedy against congatec AG, whether a claim sound in contract, warranty, tort or any other legal theory, shall be repair or replacement of the product only

# **Technical Support**

congatec AG technicians and engineers are committed to providing the best possible technical support for our customers so that our products can be easily used and implemented. We request that you first visit our website at www.congatec.com for the latest documentation, utilities and drivers, which have been made available to assist you. If you still require assistance after visiting our website then please contact our technical support department by email at support@congatec.com

### ETX<sup>®</sup> Concept and XTX<sup>™</sup> Extension

The ETX® concept is an off the shelf, multi vendor, Single-Board-Computer that integrates all the core components of a common PC and is mounted onto an application specific baseboard. ETX® modules have a standardized form factor of just 95mm x 114mm and have identical pinouts on the four system connectors. The ETX® module provides most of the functional requirements for any application. These functions include, but are not limited to, graphics, sound, keyboard/mouse, IDE, Ethernet, parallel, serial and USB ports. Four ruggedized connectors provide the baseboard interface and carry all the I/O signals to and from the ETX® module.

Baseboard designers can utilize as little or as many of the I/O interfaces as deemed necessary. The baseboard can therefore provide all the interface connectors required to attach the system to the application specific peripherals. This versatility allows the designer to create a dense and optimized package, which results in a more reliable product while simplifying system integration. Most importantly ETX® applications are scalable, which means once a product has been created there is the ability to diversify the product range through the use of different performance class ETX® modules. Simply unplug one module and replace it with another, no redesign is necessary.

XTX<sup>™</sup> is an expansion and continuation of the well-established and highly successful ETX® standard. XTX<sup>™</sup> offers the newest I/O technologies on this proven form factor. Now that the ISA bus is being used less and less in modern embedded applications congatec AG offers an array of different features on the X2 connector than those currently found on the ETX® platform. These features include new serial high speed buses such as PCI Express<sup>™</sup> and Serial ATA®. All other signals found on connectors X1, X3, and X4 remain the same in accordance to the ETX® standard (Rev. 2.7) and therefore will be completely compatible. If the embedded PC application still requires the ISA bus then an ISA bridge can be implemented on the application specific baseboard or the readily available LPC bus located on the XTX<sup>™</sup> module may be used. Please contact congatec technical support for details.

# Lead-Free Designs (RoHS)

As of July 2006 all electronic products are required to be environmentally friendly. In future, many of the currently available embedded computer modules will not be offered as lead-free variants. For this reason all congatec AG designs are created from lead-free components and are completely RoHS compliant. This makes congatec AG products ideal lead-free substitutes for new and existing designs.

#### Certification

congatec AG is certified to DIN EN ISO 9001:2000 standard.

# **Contents**

| 1 Connector Diagram                                                                 | 8  |

|-------------------------------------------------------------------------------------|----|

| 2 Specifications                                                                    | 9  |

| 2.1 Mechanical Dimensions                                                           | 9  |

| 2.2 Power Supply                                                                    |    |

| 2.3 CMOS Battery                                                                    | 10 |

| 2.4 Environmental Specifications                                                    | 10 |

| 3 Connector Description                                                             | 11 |

| 3.1 XTX Module Connector                                                            | 11 |

| 3.1.1 Connector X1 (PCI Bus, USB, Audio)                                            | 11 |

| 3.1.2 Connector X2 (PCIe, SATA, USB, ExpressCard, AC'97/HDA, LPC,)                  | 12 |

| 3.1.3 Connector X3 (VGA, LCD, Video, COM1, COM2, LPT/Floppy, IrDA, Mouse, Keyboard) |    |

| 3.1.4 Connector X4 (IDE 1, IDE 2, Ethernet, Miscellaneous)                          |    |

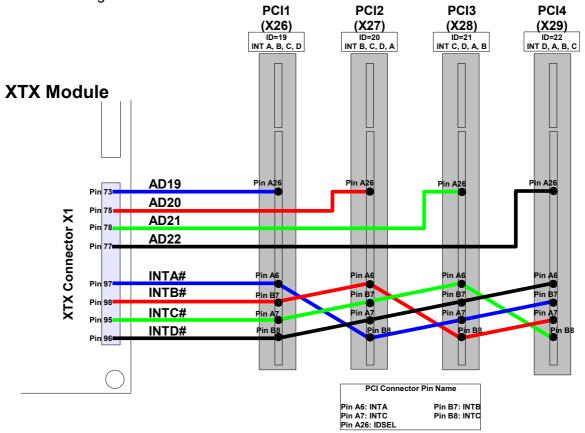

| 3.2 Subsystems of XTX Connector X1                                                  |    |

| 3.2.1 PCI Bus                                                                       |    |

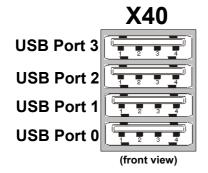

| 3.2.2 Universal Serial Bus (USB)                                                    |    |

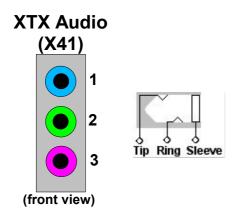

| 3.2.3 XTX Module Audio                                                              |    |

| 3.3 Subsystems of XTX Connector X2                                                  |    |

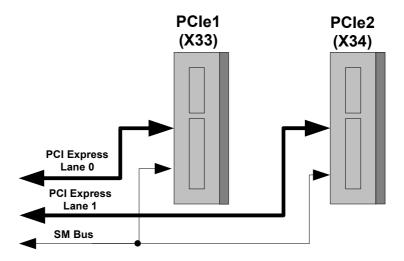

| 3.3.1 PCI Express™ x1 Connectors                                                    |    |

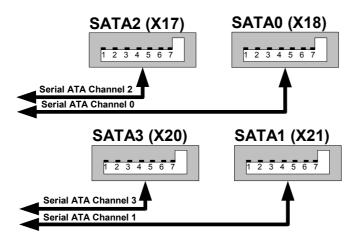

| 3.3.2 Serial ATA™                                                                   |    |

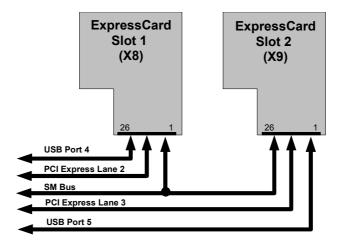

| 3.3.3 ExpressCard™                                                                  |    |

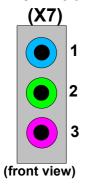

| 3.3.4 AC'97/HDA Audio                                                               |    |

| 3.3.5 Low Pin Count Bus (LPC)                                                       |    |

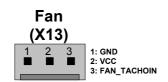

| 3.3.6 Fan Connector and Power Configuration                                         | ∠T |

|                                                                                     |    |

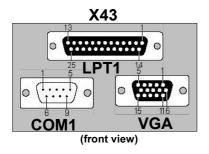

| 3.4.1 VGA Output, Serial Ports and Parallel Port / Floppy                           |    |

| 3.4.3 TV Interface                                                                  |    |

| 3.4.4 Serial Infrared Interface (IrDA)                                              |    |

| 3.4.5 PS/2 Mouse and Keyboard                                                       |    |

| 3.5 Subsystems of XTX Connector X4                                                  | 20 |

| 3.5.1 IDE                                                                           | 27 |

| 3.5.2 Ethernet                                                                      |    |

| 3.5.3 Feature Connector                                                             |    |

| 3.5.4 I2C Bus                                                                       |    |

| 4 Additional Features                                                               | 29 |

| 4.1 Reset                                                                           |    |

| 4.1 Reset 4.2 PC Speaker (Beeper)                                                   |    |

| 4.3 Debug Display                                                                   | 20 |

| 4.4 Ground Test Points                                                              |    |

|                                                                                     |    |

| 5 Mechanical Drawing conga-XEVAL                                                    | 31 |

| 6 Industry Specifications                                                           | 32 |

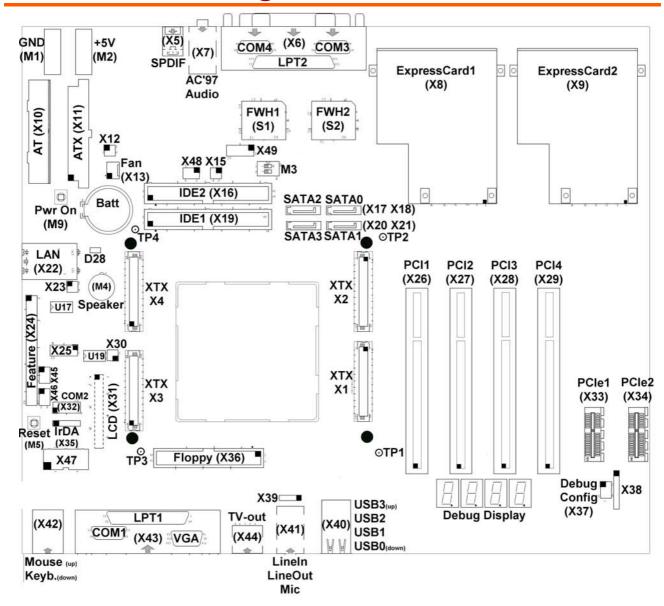

# 1 Connector Diagram

Note: Pin 1 is marked on the bottom of the XTX Evaluation Baseboard with a quadratic pad. The table below lists the connector (Con.) and page links (Page) to its description.

| Con.   | Page | Con. | Page | Con.    | Page | Con.   | Page | Con.    | Page | Con.    | Page | Con.  | Page |

|--------|------|------|------|---------|------|--------|------|---------|------|---------|------|-------|------|

| X1     | 11   | X7   | 19   | X13/X48 | 21   | X23    | 27   | X32/X43 | 22   | X39/X41 | 17   | M1-M2 | 9    |

| X2     | 12   | X8   | 18   | X15     | 19   | X24    | 28   | X33-34  | 17   | X40     | 16   | М3    | 21   |

| X3     | 13   | X9   | 18   | X16/X19 | 27   | X25    | 28   | X35     | 26   | X42     | 26   | Batt  | 10   |

| X4     | 15   | X10  | 9    | X17-18  | 18   | X26-29 | 16   | X36     | 23   | X44     | 26   | M4-5  | 29   |

| X5     | 19   | X11  | 9    | X20-21  | 18   | X30    | 22   | X37     | 30   | X45-46  | 24   | M9    | 9    |

| X6/X49 | 20   | X12  | 9    | X22     | 27   | X31    | 23   | X38     | 30   | X47     | 24   | TP1-4 | 30   |

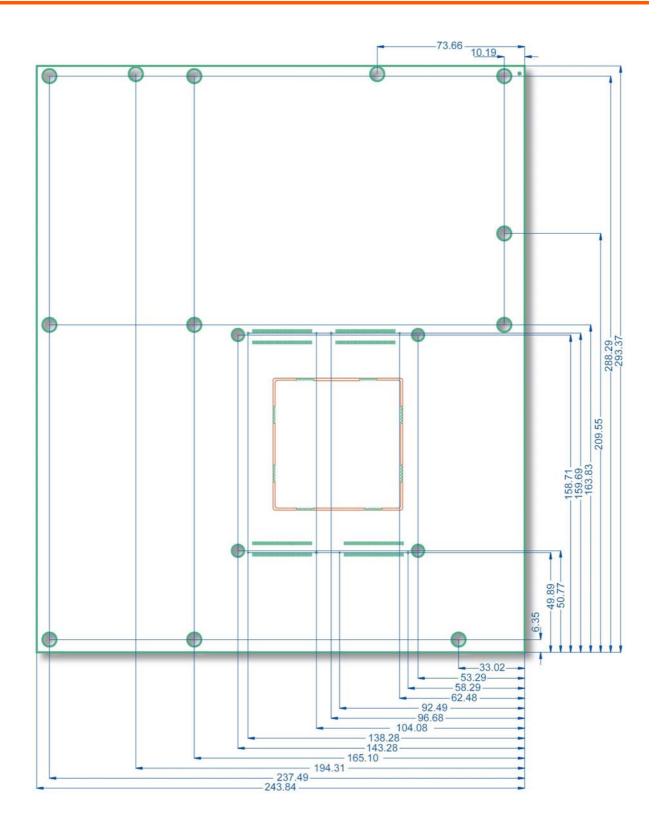

# **Specifications**

#### 2.1 **Mechanical Dimensions**

- 294.0mm x 244.0mm

- · Height approx. 44mm

#### 2.2 **Power Supply**

The XTX Evaluation baseboards can be used with standard AT (Connector X10) or ATX (Connector X11) power supplies.

When using an ATX power supply, the XTX module will start after the power-on button M9 is pressed. The ATX power supply can also be used in AT mode. In this case the module will start after the power switch on the power supply is turned on.

| Jumper X12 | Configuration                    |

|------------|----------------------------------|

|            | ATX Power supply                 |

| 3 - 4      | ATX Power supply runs in AT mode |

### **E**Connector Type

X12: 2.54mm grid jumper.

The XTX Evaluation Baseboard can also be used with 5V power supply (connector M1 and M2). In this case the +12V power supply for Fan and LCD Backlight is not available. The +3.3V used by some devices on the XTX Evaluation Baseboard is generated onboard from the 5V power supply.

| Connector | Configuration |

|-----------|---------------|

| M1        | Ground        |

| M2        | +5VDC, ±5%    |

**Connector Type**

4mm diameter plug

# 2.3 CMOS Battery

The XTX Evaluation Baseboard includes a battery that supplies the RTC and CMOS memory of the XTX CPU module. The battery needs to provide a power of 3V. The specified battery type is CR2032.

#### Warning

Danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer. Dispose of used batteries according to the manufacturer's instructions.

To fulfill the requirements of the EN60950, the XTX Evaluation Baseboard incorporates two current-limiting devices (resistor and diode) in the battery power supply path.

# 2.4 Environmental Specifications

Temperature Operation: 0° to 60°CStorage: -20° to +80°C

Humidity Operation: 10% to 90% Storage: 5% to 95%

The above operating temperatures must be strictly adhered to at all times. The maximum operating temperature refers to any measurable spot on the modules surface.

Humidity specifications are for non-condensing conditions.

# 3 Connector Description

# 3.1 XTX Module Connector

# 3.1.1 Connector X1 (PCI Bus, USB, Audio)

| Pin | Signal  | Description                    | Pin | Signal   | Description                          |

|-----|---------|--------------------------------|-----|----------|--------------------------------------|

| 1   | GND     | Power Ground                   | 2   | GND      | Power Ground                         |

| 3   | PCICLK3 | PCI Clock output 3             | 4   | PCICLK4  | PCI Clock output 4                   |

| 5   | GND     | Power Ground                   | 6   | GND      | Power Ground                         |

| 7   | PCICLK1 | PCI Clock output 1             | 8   | PCICLK2  | PCI Clock output 2                   |

| 9   | REQ3#   | PCI Bus request 3              | 10  | GNT3#    | PCI Bus grant 3                      |

| 11  | GNT2#   | PCI Bus grant 2                | 12  | 3V       | Power Supply +3.3VDC                 |

| 13  | REQ2#   | PCI Bus request 2              | 14  | GNT1#    | PCI Bus grant 1                      |

| 15  | REQ1#   | PCI Bus request 1              | 16  | 3V       | Power Supply +3.3VDC                 |

| 17  | GNT0#   | PCI Bus grant 0                | 18  | RESERVED |                                      |

| 19  | VCC     | Power Supply +5VDC, ±5%        | 20  | VCC      | Power Supply +5VDC, ±5%              |

| 21  | SERIRQ  | Serial Interrupt request       | 22  | REQ0#    | PCI Bus request 0                    |

| 23  | AD0     | PCI Address/Data bus line 0    | 24  | 3V       | Power Supply +3.3VDC                 |

| 25  | AD1     | PCI Address/Data bus line 1    | 26  | AD2      | PCI Address/Data bus line 2          |

| 27  | AD4     | PCI Address/Data bus line 4    | 28  | AD3      | PCI Address/Data bus line 3          |

| 29  | AD6     | PCI Address/Data bus line 6    | 30  | AD5      | PCI Address/Data bus line 5          |

| 31  | CBE0#   | PCI Bus command/byte enables 0 | 32  | AD7      | PCI Address/Data bus line 7          |

| 33  | AD8     | PCI Address/Data bus line 8    | 34  | AD9      | PCI Address/Data bus line 9          |

| 35  | GND     | Power Ground                   | 36  | GND      | Power Ground                         |

| 37  | AD10    | PCI Address/Data bus line 10   | 38  | AUXAL    | Audio Auxiliary input A left         |

| 39  | AD11    | PCI Address/Data bus line 11   | 40  | MIC      | Microphone input                     |

| 41  | AD12    | PCI Address/Data bus line 12   | 42  | AUXAR    | Audio Auxiliary input A right        |

| 43  | AD13    | PCI Address/Data bus line 13   | 44  | ASVCC    | Analog supply of sound controller    |

| 45  | AD14    | PCI Address/Data bus line 14   | 46  | SNDL     | Audio Line-Level stereo output left  |

| 47  | AD15    | PCI Address/Data bus line 15   | 48  | ASGND    | Analog ground of sound controller    |

| 49  | CBE1#   | PCI Bus command/byte enables 1 | 50  | SNDR     | Audio Line-Level stereo output right |

| 51  | VCC     | Power Supply +5VDC, ±5%        | 52  | VCC      | Power Supply +5VDC, ±5%              |

| 53  | PAR     | PCI Bus parity                 | 54  | SERR#    | PCI Bus system error                 |

| 55  | GPERR#  | PCI Bus grant parity error     | 56  | RESERVED |                                      |

| 57  | PME#    | PCI Bus power management event | 58  | USB2#    | USB Port 2, data - or D-             |

| 59  | LOCK#   | PCI Bus lock                   | 60  | DEVSEL#  | PCI Bus device select                |

| 61  | TRDY#   | PCI Bus target ready           | 62  | USB3#    | USB Port 3, data - or D-             |

| 63  | IRDY#   | PCI Bus initiator ready        | 64  | STOP#    | PCI Bus stop                         |

| 65  | FRAME#  | PCI Bus frame                  | 66  | USB2     | USB Port 2, data + or D+             |

| 67  | GND     | Power Ground                   | 68  | GND      | Power Ground                         |

| 69  | AD16    | PCI Address/Data bus line 16   | 70  | CBE2#    | PCI Bus command/byte enables 2       |

| 71  | AD17    | PCI Address/Data bus line 17   | 72  | USB3     | USB Port 3, data + or D+             |

| 73  | AD19    | PCI Address/Data bus line 19   | 74  | AD18     | PCI Address/Data bus line 18         |

| 75  | AD20    | PCI Address/Data bus line 20   | 76  | USB0#    | USB Port 0, data - or D-             |

| 77  | AD22    | PCI Address/Data bus line 22   | 78  | AD21     | PCI Address/Data bus line 21         |

| 79  | AD23    | PCI Address/Data bus line 23   | 80  | USB1#    | USB Port 1, data - or D-             |

| 81  | AD24    | PCI Address/Data bus line 24   | 82  | CBE3#    | PCI Bus command/byte enables 3       |

| 83  | VCC     | Power Supply +5VDC, ±5%        | 84  | VCC      | Power Supply +5VDC, ±5%              |

| 85  | AD25    | PCI Address/Data bus line 25   | 86  | AD26     | PCI Address/Data bus line 26         |

| 87  | AD28    | PCI Address/Data bus line 28   | 88  | USB0     | USB Port 0, data + or D+             |

| 89  | AD27    | PCI Address/Data bus line 27   | 90  | AD29     | PCI Address/Data bus line 29         |

| 91  | AD30    | PCI Address/Data bus line 30   | 92  | USB1     | USB Port 1, data + or D+             |

| 93  | PCIRST# | PCI Bus reset                  | 94  | AD31     | PCI Address/Data bus line 31         |

| 95  | INTC#   | PCI Bus interrupt C            | 96  | INTD#    | PCI Bus interrupt D                  |

| 97  | INTA#   | PCI Bus interrupt A            | 98  | INTB#    | PCI Bus interrupt B                  |

| 99  | GND     | Power Ground                   | 100 | GND      | Power Ground                         |

# 3.1.2 Connector X2 (PCIe, SATA, USB, ExpressCard, AC'97/HDA, LPC, ...)

| Pin      | Signal         | Description                                            | Pin | Signal          | Description                                                            |

|----------|----------------|--------------------------------------------------------|-----|-----------------|------------------------------------------------------------------------|

| 1        | GND            | Power Ground                                           | 2   | GND             | Power Ground                                                           |

| 3        | PCIF CLK RFF+  | PCI Express Reference Clock,                           | 4   | SATA0 RX+       | Serial ATA channel 0,                                                  |

| Ū        | I OIL_OLK_IKLI | positive differential line                             |     | 0, 11, 10_1 0 1 | receive input, positive diff. line                                     |

| 5        | PCIE CLK REF-  | PCI Express Reference Clock,                           | 6   | SATA0 RX-       | Serial ATA channel 0,                                                  |

| •        | . 0.1_01.1     | negative differential line                             |     |                 | receive input, negative diff. line                                     |

| 7        | GND            | Power Ground                                           | 8   | GND             | Power Ground                                                           |

| 9        | PCIE3 TX+      | PCI Express lane 3,                                    | 10  | SATA0 TX-       | Serial ATA channel 0,                                                  |

|          | . 0.20         | transmit output, positive line                         | . • | 0,0             | transmit output, negative diff. line                                   |

| 11       | PCIE3 TX-      | PCI Express lane 3,                                    | 12  | SATA0 TX+       | Serial ATA channel 0,                                                  |

|          |                | transmit output, negative line                         |     |                 | transmit output, positive diff. line                                   |

| 13       | GND            | Power Ground                                           | 14  | 5V SB           | Supply of internal suspend circuit                                     |

| 15       | PCIE3 RX+      | PCI Express lane 3,                                    | 16  | SATA1 RX+       | Serial ATA channel 1,                                                  |

|          | _              | receive input, positive line                           |     | _               | receive input, positive diff. line                                     |

| 17       | PCIE3_RX-      | PCI Express lane 3,                                    | 18  | SATA1 RX-       | Serial ATA channel 1,                                                  |

|          | _              | receive input, negative line                           |     | _               | receive input, negative diff. line                                     |

| 19       | VCC            | Power Supply +5VDC, ±5%                                | 20  | 5V SB           | Supply of internal suspend circuit                                     |

| 19<br>21 | EXC1 CPPE#     | ExpressCard capable card                               | 22  | SATA1 TX-       | Serial ATA channel 1,                                                  |

|          | _              | request for slot 2                                     |     | _               | transmit output, negative diff. line                                   |

| 23       | EXC1_RST#      | ExpressCard Reset for slot 2                           | 24  | SATA1_TX+       | Serial ATA channel 1,                                                  |

|          | _              | ·                                                      |     | _               | transmit output, positive diff. line                                   |

| 25       | USBP5          | Universal Serial Bus Port 5,                           | 26  | GND             | Power Ground                                                           |

|          |                | positive differential line                             |     |                 |                                                                        |

| 27       | USBP5#         | Universal Serial Bus Port 5,                           | 28  | SATA2_RX+       | Serial ATA channel 2,                                                  |

|          |                | negative differential line                             |     |                 | receive input, positive diff. line                                     |

| 29       | GND            | Power Ground                                           | 30  | SATA2_RX-       | Serial ATA channel 2,                                                  |

|          |                |                                                        |     |                 | receive input, negative diff. line                                     |

| 31       | PCIE2_TX+      | PCI Express lane 2,                                    | 32  | SUS_STAT#       | Suspend Status                                                         |

|          |                | transmit output, positive diff. line                   |     |                 |                                                                        |

| 33       | PCIE2_TX-      | PCI Express lane 2,                                    | 34  | RESERVED        | N.C.                                                                   |

|          |                | transmit output, negative diff. line                   |     |                 |                                                                        |

| 35       | GND            | Power Ground                                           | 36  | GND             | Power Ground                                                           |

| 37       | PCIE2_RX+      | PCI Express lane 2,                                    | 38  | SATA2_TX-       | Serial ATA channel 2,                                                  |

|          |                | receive input, positive diff. line                     |     |                 | transmit output, negative diff. line                                   |

| 39       | PCIE2_RX-      | PCI Express lane 2,                                    | 40  | SATA2_TX+       | Serial ATA channel 2,                                                  |

|          | =>/00 000=#    | receive input, negative diff. line                     |     | 0.115           | transmit output, positive diff. line                                   |

| 41       | EXC0_CPPE#     | ExpressCard capable card                               | 42  | GND             | Power Ground                                                           |

|          | =>/00 =0=#     | request for slot 1                                     |     | 0.7.0           |                                                                        |

| 43       | EXC0_RST#      | ExpressCard Reset for slot 1                           | 44  | SATA3_RX+       | Serial ATA channel 3,                                                  |

|          | LIODD 4        | 10 : 10 : 1                                            | 40  | 0.4.7.4.0. DV   | receive input, positive diff. line                                     |

| 45       | USBP4          | Universal Serial Bus Port 4,                           | 46  | SATA3_RX-       | Serial ATA channel 3,                                                  |

| 47       | LIODD 4#       | positive differential line                             | 40  | WETDIO          | receive input, negative diff. line                                     |

| 47       | USBP4#         | Universal Serial Bus Port 4,                           | 48  | WDTRIG          | Watch Dog Trigger input                                                |

| 40       | OLD 00#        | negative differential line                             |     | CATALED#        | Opinial ATA patients LED                                               |

| 49       | SLP_S3#        | S3 (Suspend to RAM) Sleep                              | 50  | SATALED#        | Serial ATA activity LED                                                |

| 51       | VCC            | Control  Power Supply +5VDC +5%                        | 52  | VCC             | Dower Supply +5\/DC +50/                                               |

|          |                | Power Supply +5VDC, ±5%                                |     |                 | Power Supply +5VDC, ±5%                                                |

| 53       | PCIE1_RX-      | PCI Express lane 1, receive input, negative diff. line | 54  | SATA3_TX-       | Serial ATA channel 3,                                                  |

| 55       | PCIE1 RX+      |                                                        | 56  | SATA3 TX+       | transmit output, negative diff. line Serial ATA channel 3,             |

| 55       | POIE I_RAT     | PCI Express lane 1,                                    | 50  | SATAS_TAT       |                                                                        |

| 57       | GND            | receive input, positive diff. line Power Ground        | 58  | IL SATA#        | transmit output, positive diff. line Serial ATA Interlock Switch Input |

| 57<br>59 | PCIE1_TX-      | PCI Express lane 1,                                    | 60  | RESERVED        | N.C.                                                                   |

| Ja       | 011 1 1 1 1 1  | transmit output, negative diff. line                   | 00  | INCOLINACIO     | 14.0.                                                                  |

| 61       | PCIE1 TX+      | PCI Express lane 1,                                    | 62  | RESERVED        | N.C.                                                                   |

| ΟI       | I OIL I_IAT    | transmit output, positive diff. line                   | 02  | INCOLINACIO     | 14.0.                                                                  |

| 63       | PCE WAKE#      | PCI Express Wake Event                                 | 64  | PCI GNT#A       | Reserved                                                               |

| 65       | RESERVED       | N.C.                                                   | 66  | PCI_GNT#A       | Reserved                                                               |

| 67       | GND            | Power Ground                                           | 68  | GND             | Power Ground                                                           |

| 69       | PCIE0 RX-      | PCI Express channel 0,                                 | 70  | RESERVED        | N.C.                                                                   |

| UU       | I OILO_IVV-    | i oi Express chariller 0,                              | 10  | INCOLINACIO     | [14.O.                                                                 |

| receive input, negative diff. line  71 PCIEO_RX+ PCI Express channel 0, receive input, positive line  73 GND Power Ground 74 VCC Power Supply +5VDC, ±5%  75 PCIEO_TX- PCI Express channel 0, transmit output, negative line  77 PCIEO_TX+ PCI Express channel 0, transmit output, positive line  78 RESERVED N.C.  79 CODECSET AC'97/HDA Disable onboard Audio Codec  81 AC_RST# AC'97/HDA CODEC Reset 82 AC_SDOUT AC'97/HDA Audio Serial Data Output to CODEC  83 VCC Power Supply +5VDC, ±5%  84 VCC Power Supply +5VDC, ±5%  85 AC_SYNC AC'97/HDA Serial Bus 86 AC_SDINO AC'97/HDA Audio Serial Data Input from CODEC0  87 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC1  89 AC_BIT_CLK AC'97/HDA 12.228 MHz Serial Bit 90 FAN_TACHOIN Fan tachometer input Clock from CODEC  91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0  93 LPC_AD1 LPC Multiplexed Command, Address and Data line 0  94 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  PCI Express channel 0, 72 RESERVED N.C.  Power Supply +5VDC, ±5%  AC_SPIND AC'97/HDA Audio Serial Data Output to CODEC  Power Supply +5VDC, ±5%  AC_SDINO AC'97/HDA Audio Serial Data Input from CODEC0  PAN_TACHOIN Fan tachometer input Clock from CODEC  PAN_PWMOUT Fan speed control  PC Frame: Indicates start of a new or termination of a broken cycle or termination of a broken cycle PC_AD2 LPC Multiplexed Command, Address and Data line 1  PC Frame: Indicates start of a new or termination of a broken cycle PC_DRQ0# LPC Encoded DMA/Bus Master Request line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin  | Signal     | Description                     | Pin  | Signal      | Description                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|---------------------------------|------|-------------|-------------------------------------|

| 71 PCIE0_RX+ PCI Express channel 0, receive input, positive line 73 GND Power Ground 74 VCC Power Supply +5VDC, ±5% 75 PCIE0_TX- PCI Express channel 0, transmit output, negative line 76 RESERVED N.C. 77 PCIE0_TX+ PCI Express channel 0, transmit output, positive line 78 RESERVED N.C. 79 CODECSET AC'97/HDA Disable onboard Audio Codec 81 AC_RST# AC'97/HDA CODEC Reset 82 AC_SDOUT AC'97/HDA Audio Serial Data Output to CODEC 83 VCC Power Supply +5VDC, ±5% 85 AC_SYNC AC'97/HDA Serial Bus 86 AC_SDINO AC'97/HDA Audio Serial Data Input Synchronization 87 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC0 88 AC_BIT_CLK AC'97/HDA Audio Serial Bit 90 FAN_TACHOIN Fan tachometer input 89 AC_BIT_CLK AC'97/HDA Serial Bit 00 FAN_TACHOIN Fan tachometer input 80 Clock from CODEC 81 AC_SDIN1 LPC_AD0 LPC Multiplexed Command, Address and Data line 0 81 LPC_AD1 LPC Multiplexed Command, Address and Data line 0 82 LPC_AD2 LPC Multiplexed Command, Address and Data line 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FIII | Signal     |                                 | HIII | Sigilal     | Description                         |

| receive input, positive line  73 GND Power Ground 74 VCC Power Supply +5VDC, ±5%  75 PCIE0_TX- PCI Express channel 0, transmit output, negative line  76 RESERVED N.C.  77 PCIE0_TX+ PCI Express channel 0, transmit output, positive line  78 RESERVED N.C.  79 CODECSET AC'97/HDA Disable onboard Audio Codec  81 AC_RST# AC'97/HDA CODEC Reset 82 AC_SDOUT AC'97/HDA Audio Serial Data Output to CODEC  83 VCC Power Supply +5VDC, ±5% 84 VCC Power Supply +5VDC, ±5%  85 AC_SYNC AC'97/HDA Serial Bus 86 AC_SDIN0 AC'97/HDA Audio Serial Data Input from CODEC0  87 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC1  88 AC_BIT_CLK AC'97/HDA 12.228 MHz Serial Bit 90 FAN_TACHOIN Fan tachometer input Clock from CODEC  91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0  92 FAN_PWMOUT Fan speed control  93 LPC_AD1 LPC Multiplexed Command, Address and Data line 1  95 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  POWER Supply +5VDC, ±5%  86 RESERVED N.C.  87 RESERVED N.C.  88 RESERVED N.C.  80 RESERVED N.C.  81 AC'97/HDA dudio Serial Data Output for Output to CODEC Power Supply +5VDC, ±5%  81 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC0  81 FAN_TACHOIN Fan tachometer input from CODEC2  82 FAN_PWMOUT Fan speed control  83 LPC_AD1 LPC Multiplexed Command, Address and Data line 1  84 PC_FRAME# LPC Frame: Indicates start of a new or termination of a broken cycle  85 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  86 PC_DRQ0# LPC Encoded DMA/Bus Master  87 RESERVED N.C.                                                                                                                                                 | 74   | DOLEG DV   |                                 | 70   | DECEDVED    | N.C.                                |

| Power Ground   Powe   | 71   | PCIEU_RX+  |                                 | 12   | RESERVED    | N.C.                                |

| 75 PCIEO_TX- PCI Express channel 0, transmit output, negative line 77 PCIEO_TX+ PCI Express channel 0, transmit output, negative line 78 RESERVED N.C.  79 CODECSET AC 97/HDA Disable onboard Audio Codec 81 AC_RST# AC 97/HDA CODEC Reset 82 AC_SDOUT AC 97/HDA Audio Serial Data Output to CODEC 83 VCC Power Supply +5VDC, ±5% 84 VCC Power Supply +5VDC, ±5% Output to CODEC 85 AC_SYNC AC 97/HDA Serial Bus 86 AC_SDINO AC 97/HDA Audio Serial Data Input from CODEC0 87 AC_SDIN1 AC 97/HDA Audio Serial Data Input from CODEC1 88 AC_BIT_CLK AC 97/HDA 12.228 MHz Serial Bit 90 FAN_TACHOIN Fan tachometer input Clock from CODEC 91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0 93 LPC_AD1 LPC Multiplexed Command, Address and Data line 1 95 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  PCI Express channel 0, 78 RESERVED N.C.  8                                                                                                                        | 70   | OND        |                                 | 7.4  | 1/00        | D                                   |

| transmit output, negative line  77 PCIEO_TX+ PCI Express channel 0, transmit output, positive line  78 RESERVED N.C.  79 CODECSET AC'97/HDA Disable onboard Audio Codec  81 AC_RST# AC'97/HDA CODEC Reset 82 AC_SDOUT AC'97/HDA Audio Serial Data Output to CODEC  83 VCC Power Supply +5VDC, ±5% 84 VCC Power Supply +5VDC, ±5% AC_SYNC AC'97/HDA Serial Bus Synchronization 86 AC_SDINO AC'97/HDA Audio Serial Data Input from CODEC0  87 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC1  89 AC_BIT_CLK AC'97/HDA 12.228 MHz Serial Bit 90 FAN_TACHOIN Fan tachometer input Clock from CODEC  91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0  93 LPC_AD1 LPC Multiplexed Command, Address and Data line 1  95 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  178 RESERVED N.C.  80 N.C.  80 N.C.  81 RESERVED N.C.  82 RESERVED N.C.  84 VCC Power Supply +5VDC, ±5%  85 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC  86 AC_SDIN0 AC'97/HDA Audio Serial Data Input from CODEC2  87 FAN_TACHOIN Fan tachometer input Fan speed control Address and Data line 0  98 LPC_AD1 LPC Multiplexed Command, Address and Data line 1  99 LPC_AD2 LPC Multiplexed Command, Address and Data line 1  90 LPC_DRQ0# LPC Encoded DMA/Bus Master Request line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /3   |            |                                 |      |             |                                     |

| 77 PCIEO_TX+ PCI Express channel 0, transmit output, positive line  78 RESERVED N.C.  79 CODECSET AC'97/HDA Disable onboard Audio Codec  81 AC_RST# AC'97/HDA CODEC Reset 82 AC_SDOUT AC'97/HDA Audio Serial Data Output to CODEC  83 VCC Power Supply +5VDC, ±5% 84 VCC Power Supply +5VDC, ±5% Output to CODEC  85 AC_SYNC AC'97/HDA Serial Bus Synchronization 86 AC_SDINO AC'97/HDA Audio Serial Data Input from CODEC0  87 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC1  89 AC_BIT_CLK AC'97/HDA 12.228 MHz Serial Bit Olock from CODEC2  91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0  92 FAN_PWMOUT Fan speed control Address and Data line 1  94 LPC_FRAME# LPC Frame: Indicates start of a new or termination of a broken cycle PC_DRQ0# LPC Encoded DMA/Bus Master Request line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75   | PCIE0_TX-  |                                 | 76   | RESERVED    | N.C.                                |

| transmit output, positive line  79  CODECSET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |            |                                 |      |             |                                     |

| 79 CODECSET AC`97/HDA Disable onboard Audio Codec  81 AC_RST# AC'97/HDA CODEC Reset 82 AC_SDOUT AC'97/HDA Audio Serial Data Output to CODEC  83 VCC Power Supply +5VDC, ±5% 84 VCC Power Supply +5VDC, ±5%  85 AC_SYNC AC'97/HDA Serial Bus 86 AC_SDINO AC'97/HDA Audio Serial Data Input From CODEC0  87 AC_SDIN1 AC'97/HDA Audio Serial Data Input Input from CODEC1  89 AC_BIT_CLK AC'97/HDA 12.228 MHz Serial Bit 90 FAN_TACHOIN Fan tachometer input Clock from CODEC  91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0  93 LPC_AD1 LPC Multiplexed Command, Address and Data line 1  95 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  86 AC_SDIN0 AC'97/HDA Audio Serial Data Input from CODEC2  87 FAN_PWMOUT Fan speed control Fan speed control Address and Data line 0  88 AC_SDIN2 AC'97/HDA Fan tachometer input Fan speed control Fa | 77   | PCIE0_TX+  |                                 | 78   | RESERVED    | N.C.                                |

| Audio Codec  81 AC_RST# AC'97/HDA CODEC Reset 82 AC_SDOUT AC'97/HDA Audio Serial Data Output to CODEC  83 VCC Power Supply +5VDC, ±5% 84 VCC Power Supply +5VDC, ±5% 85 AC_SYNC AC'97/HDA Serial Bus Synchronization 86 AC_SDIN0 AC'97/HDA Audio Serial Data Input From CODEC0  87 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC1  89 AC_BIT_CLK AC'97/HDA 12:228 MHz Serial Bit Science Bit S |      |            |                                 |      |             |                                     |

| AC_RST#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 79   | CODECSET   | AC`97/HDA Disable onboard       | 80   | VCC         | Power Supply +5VDC, ±5%             |

| Supply +5VDC, ±5%   Supp   |      |            |                                 |      |             |                                     |

| Solution   Power Supply +5VDC, ±5%   84   VCC   Power Supply +5VDC, ±5%   85   AC_SYNC   AC'97/HDA Serial Bus   86   AC_SDIN0   AC'97/HDA Audio Serial Data Input   From CODEC0   AC'97/HDA Audio Serial Data Input   From CODEC0   AC'97/HDA Audio Serial Data Input   From CODEC2   AC'97/HDA 12.228 MHz Serial Bit   90   FAN_TACHOIN   Fan tachometer input   Fan tachometer input   Fan tachometer input   Fan speed control   Address and Data line 0   Address and Data line 1   Address and Data line 2   FRAME#   LPC Frame: Indicates start of a new or termination of a broken cycle   LPC_AD2   LPC Multiplexed Command, Address and Data line 2   Address and Data line 2   Address Input   LPC_BRQ0#   LPC_Encoded DMA/Bus Master   Request line 0   Request line   Reque   | 81   | AC_RST#    | AC'97/HDA CODEC Reset           | 82   | AC_SDOUT    | AC'97/HDA Audio Serial Data         |

| 85 AC_SYNC  AC'97/HDA Serial Bus Synchronization  86 AC_SDIN0  AC'97/HDA Audio Serial Data Input from CODEC0  87 AC_SDIN1  AC'97/HDA Audio Serial Data Input from CODEC1  88 AC_SDIN2  AC'97/HDA Audio Serial Data Input from CODEC2  89 AC_BIT_CLK  AC'97/HDA 12.228 MHz Serial Bit Clock from CODEC  91 LPC_AD0  LPC Multiplexed Command, Address and Data line 0  93 LPC_AD1  LPC Multiplexed Command, Address and Data line 1  PC Multiplexed Command, Address and Data line 1  96 LPC_DRQ0#  LPC Encoded DMA/Bus Master Request line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | _          |                                 |      | _           | Output to CODEC                     |

| AC_SYNC   AC'97/HDA Serial Bus   Synchronization   Synchronization   AC_SDIN0   AC'97/HDA Audio Serial Data Input from CODEC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83   | VCC        | Power Supply +5VDC, ±5%         | 84   | VCC         | Power Supply +5VDC, ±5%             |

| Synchronization from CODEC0  87 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC1 AC'97/HDA Audio Serial Data Input from CODEC1  89 AC_BIT_CLK AC'97/HDA 12.228 MHz Serial Bit OCIOCK from CODEC  91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0  93 LPC_AD1 LPC Multiplexed Command, Address and Data line 1  95 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  Synchronization from CODEC  FAN_TACHOIN Fan tachometer input Fan speed control  FAN_PWMOUT Fan speed control  LPC Frame: Indicates start of a new or termination of a broken cycle  LPC_AD2 LPC Multiplexed Command, Address and Data line 2  Synchronization from CODEC0  FAN_TACHOIN Fan tachometer input Fan speed control  LPC Frame: Indicates start of a new or termination of a broken cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85   | AC SYNC    | AC'97/HDA Serial Bus            | 86   | AC SDIN0    | AC'97/HDA Audio Serial Data Input   |

| 87 AC_SDIN1 AC'97/HDA Audio Serial Data Input from CODEC1  89 AC_BIT_CLK AC'97/HDA 12.228 MHz Serial Bit OCIOCK from CODEC  91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0  93 LPC_AD1 LPC Multiplexed Command, Address and Data line 1  95 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  88 AC_SDIN2 AC'97/HDA Audio Serial Data Input from CODEC  FAN_TACHOIN Fan tachometer input Fan speed control  FAN_PWMOUT Fan speed control  FAN_PWMOUT Fan speed control  LPC Frame: Indicates start of a new or termination of a broken cycle  LPC_AD2 LPC Multiplexed Command, Address and Data line 2  LPC_DRQ0# LPC_Encoded DMA/Bus Master Request line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | _          | Synchronization                 |      |             | from CODEC0                         |

| Input from CODEC1   from CODEC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87   | AC SDIN1   | AC'97/HDA Audio Serial Data     | 88   | AC SDIN2    | AC'97/HDA Audio Serial Data Input   |

| Clock from CODEC  91 LPC_AD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | _          |                                 |      |             |                                     |

| Clock from CODEC  91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0  93 LPC_AD1 LPC Multiplexed Command, Address and Data line 1  95 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  Clock from CODEC  92 FAN_PWMOUT Fan speed control  LPC Frame: Indicates start of a new or termination of a broken cycle  PS LPC_AD2 LPC Multiplexed Command, Address and Data line 2  Clock from CODEC  PS LPC_AD0 LPC FRAME# LPC Frame: Indicates start of a new or termination of a broken cycle  LPC_DRQ0# LPC_Encoded DMA/Bus Master  Request line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89   | AC BIT CLK | AC'97/HDA 12.228 MHz Serial Bit | 90   | FAN TACHOIN | Fan tachometer input                |

| 91 LPC_AD0 LPC Multiplexed Command, Address and Data line 0  93 LPC_AD1 LPC Multiplexed Command, Address and Data line 1  94 LPC_FRAME# LPC Frame: Indicates start of a new or termination of a broken cycle  95 LPC_AD2 LPC Multiplexed Command, Address and Data line 2  96 LPC_DRQ0# LPC Encoded DMA/Bus Master Request line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |            |                                 |      | _           | '                                   |

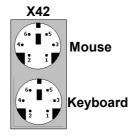

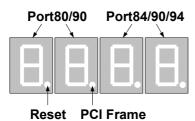

| Address and Data line 0  93 LPC_AD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 91   | LPC AD0    |                                 | 92   | FAN PWMOUT  | Fan speed control                   |