# conga-QMX6

Qseven® 2.1 Module with NXP® i.MX6 Processors

## User's Guide

Revision 1.4

# **Revision History**

| Revision | Date (yyyy.mm.dd) | Author | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1      | 2013.03.28        | AEM    | Preliminary release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0.2      | 2013.11.05        | AEM    | <ul> <li>Corrected the LVDS data rates/resolutions supported in sections 2.1 "Feature List" and 5.8 "LVDS".</li> <li>Added information about the Atheros Quadcomm Ethernet PHY for conga-QMX6 revision B.0 in sections 2.1 "Feature List" and 5.3 "Gigabit Ethernet".</li> <li>Updated section 4 "Heatspreader". Added additional heatspreader variants.</li> <li>Updated section 5.2 "UART". Updated section 5.13 "Manufacturing/Jtag Interface".</li> <li>Added pin descriptions for the onboard UART connector and the RS-232 adapter cable in section 10.1 "UART/RS-232 Debug Port".</li> <li>Added section 10.3 "JTAG Interface".</li> </ul>                                            |

| 0.3      | 2014.02.28        | AEM    | <ul> <li>Added the new Ethernet PHY (Qualcomm Atheros) for conga-QMX6 revision B.x to relevant sections.</li> <li>Changed the eMMC value of industrial variants from 2G to 4G.</li> <li>Deleted the row "RSVD" from table 23 " Manufacturing Signal Description".</li> <li>Edited section 5.2 "UART" and added caution statement.</li> <li>Corrected the pin number of signal DP_HDMI_HPD# in section 9.9 "DisplayPort".</li> <li>Updated the whole document.</li> </ul>                                                                                                                                                                                                                     |

| 1.0      | 2015.09.03        | AEM    | <ul> <li>Updated section 2.2 "Supported Operating Systems".</li> <li>Added note to table 7 "UART Signal Descriptions".</li> <li>Corrected the DP_HDMI_HPD# pin description in table 14 "DisplayPort".</li> <li>Corrected the LPC/GPIO6 (Pin 191) signal description in table 16 "LPC/GPIO".</li> <li>Changed Pin 56 from "RSVD" to "USB_VBUS_DRIVE" in various sections.</li> <li>Updated table 10 "USB 2.0 Signal Description" in compliance with the Qseven 2.0 Specification, Errata Document 1.0.</li> <li>Added table 28 "MIPI Signal Descriptions" and updated section 10.2 "MIPI/CMOS Camera".</li> <li>Updated document to revision B.x and C.x</li> <li>Official release</li> </ul> |

| 1.1      | 2016.05.04        | AEM    | <ul> <li>Updated the Options Information table in section 1 "Introduction". Also added Options Information table for revision C.x</li> <li>Updated section 2.3 "Mechanical Dimensions".</li> <li>Updated section 4 "Heatspreader".</li> <li>Replaced "Freescale" with "NXP" in the whole document.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |

| 1.2      | 2020.01.10        | BEU    | <ul> <li>Updated table references throughout the document</li> <li>Updated information about handling electrostatic sensitive devices in preface section</li> <li>Added new variant "PN:016318" to table 4</li> <li>Updated section 4 "Heatspreader"</li> <li>Updated reference to power supply design guide in section 5.14 "Power Control"</li> <li>Added note about min. pulse width to several button signals in table 23 and 24</li> <li>Added note about WDOUT signal below table 25</li> <li>Updated section 11 "Industry Specifications"</li> <li>Added information and note to section 10.7 "eMMC"</li> </ul>                                                                       |

|     | 1          |     |                                                                                                            |

|-----|------------|-----|------------------------------------------------------------------------------------------------------------|

| 1.3 | 2022.10.25 | BEU | Updated document to revision D.x                                                                           |

|     |            |     | Updated congatec AG to congatec GmbH throughout the document                                               |

|     |            |     | Added software license information to preface section                                                      |

|     |            |     | Restructured preface section                                                                               |

|     |            |     | Updated section 1 "Introduction"                                                                           |

|     |            |     | Updated table 7 "Feature Summary"                                                                          |

|     |            |     | Added module variant 016318 to table 8 "Cooling Solution Variants"                                         |

|     |            |     | Updated supported operating systems in section 2.2 "Supported Operating Systems"                           |

|     |            |     | Added module variants to section 2.5 "Power Consumption"                                                   |

|     |            |     | Updated storage temperature for commercial variants in section 2.7 "Environmental Specifications"          |

|     |            |     | Updated block diagram in section 3 "Block Diagram"                                                         |

|     |            |     | Added note about revision D.x onboard PCIe clock generator in section 5.1 "PCI Express™"                   |

|     |            |     | Added revision D.x transceiver in section 5.3 "Gigabit Ethernet"                                           |

|     |            |     | Added UARTO_RTS# and UARTO_CTS# assembly options to table 10 "Edge Finger Pinout"                          |

|     |            |     | Added revision D.x UARTO_CTS# and UARTO_RTS# information to note below table 12 "UART Signal Descriptions" |

|     |            |     | Updated USB_ID and USB_OTG_PEN signals descriptions in table 15                                            |

|     |            |     | Added revision D.x information to section 10.2 "MIPI/CMOS Camera"                                          |

|     |            |     | Renamed section 10.6 "DDR3 Memory" to "DD3RL Memory" and updated it                                        |

|     |            |     | Added revision D.x support for 1.8V micro SD cards to section 10.2 "Micro SD"                              |

|     |            |     | Removed section 11 "Industry Specifications"                                                               |

| 1.4 | 2023.12.23 | BEU | Updated title page                                                                                         |

|     |            |     | Updated RoHS Directive in preface section                                                                  |

|     |            |     | Removed revision D.x throughout the document                                                               |

|     |            |     | Added E.x to note in section 1 "Introduction"                                                              |

|     |            |     | Removed Gen 2 from PCIe in section 2.1 "Feature List" and 3 "Block Diagram"                                |

|     |            |     | Added note regarding long-term storage to section 2.7 "Environmental Specifications"                       |

|     |            |     | Added note regarding long-term storage to section 4 "Heatspreader"                                         |

|     |            |     | Updated section 5.1 "PCI Express"                                                                          |

|     |            |     | Added revision E.x to section 5.3 "Gigabit Ethernet"                                                       |

|     |            |     | Added comment for PCIe Clock signals to table 11                                                           |

|     |            |     | Added revision E.x to note under table 12 "UART Signal Descriptions"                                       |

|     |            |     | Added revision E.x to section 10.2 "MIPI/CMOS Camera"                                                      |

|     |            |     | Added revision E.x to section 10.7 "eMMC"                                                                  |

|     |            |     | Added revision E.x to section 10.8 "Micro SD"                                                              |

## **Preface**

This user's guide provides information about the components, features, connectors and signals available on the conga-QMX6 Revision E.x. It is one of four documents that you should refer to when designing an NXP® i.MX6 based Qseven® application. The other reference documents that should be used include the following:

Oseven® Design Guide

Qseven® Specification

NXP® i.MX6 Applications Processor Reference Manual (available at www.nxp.com)

The links to these documents can be found on the congatec GmbH website at www.congatec.com

#### **Software Licenses**

#### **Notice Regarding Open Source Software**

The congatec products contain Open Source software that has been released by programmers under specific licensing requirements such as the "General Public License" (GPL) Version 2 or 3, the "Lesser General Public License" (LGPL), the "ApacheLicense" or similar licenses.

You can find the specific details at https://www.congatec.com/en/licenses/.

Enter the following command "license" in the bootloader to get the complete product related license information.

To the extent that any accompanying material such as instruction manuals, handbooks etc. contain copyright notices, conditions of use or licensing requirements that contradict any applicable Open Source license, these conditions are inapplicable. The use and distribution of any Open Source software contained in the product is exclusively governed by the respective Open Source license.

The Open Source software is provided by its programmers without ANY WARRANTY, whether implied or expressed, of any fitness for a particular purpose, and the programmers DECLINE ALL LIABILITY for damages, direct or indirect, that result from the use of this software.

congatec's liability with regards to the open source Software is as set out in congatec's Software License Information.

#### Disclaimer

The information contained within this user's guide, including but not limited to any product specification, is subject to change without notice.

congatec GmbH provides no warranty with regard to this user's guide or any other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to any of the foregoing. congatec GmbH assumes no liability for any damages incurred directly or indirectly from any technical or typographical errors or omissions contained herein or for discrepancies between the product and the user's guide. In no event shall congatec GmbH be liable for any incidental, consequential, special, or exemplary damages, whether based on tort, contract or otherwise, arising out of or in connection with this user's guide or any other information contained herein or the use thereof.

#### Intended Audience

This user's guide is intended for technically qualified personnel. It is not intended for general audiences.

#### **RoHS** Directive

All congatec GmbH designs comply with EU RoHS Directive 2011/65/EU and Delegated Directive 2015/863.

#### **Electrostatic Sensitive Device**

All congatec GmbH products are electrostatic sensitive devices. They are enclosed in static shielding bags, and shipped enclosed in secondary packaging (protective packaging). The secondary packaging does not provide electrostatic protection.

Do not remove the device from the static shielding bag or handle it, except at an electrostatic-free workstation. Also, do not ship or store electronic devices near strong electrostatic, electromagnetic, magnetic, or radioactive fields unless the device is contained within its original packaging. Be aware that failure to comply with these guidelines will void the congatec GmbH Limited Warranty.

## **Symbols**

The following symbols are used in this user's guide:

#### Warning

Warnings indicate conditions that, if not observed, can cause personal injury.

#### Caution

Cautions warn the user about how to prevent damage to hardware or loss of data.

Notes call attention to important information that should be observed.

## Copyright Notice

Copyright © 2013, congatec GmbH. All rights reserved. All text, pictures and graphics are protected by copyrights. No copying is permitted without written permission from congatec GmbH.

congatec GmbH has made every attempt to ensure that the information in this document is accurate yet the information contained within is supplied "as-is".

#### **Trademarks**

Product names, logos, brands, and other trademarks featured or referred to within this user's guide, or the congatec website, are the property of their respective trademark holders. These trademark holders are not affiliated with congatec GmbH, our products, or our website.

### Warranty

congatec GmbH makes no representation, warranty or guaranty, express or implied regarding the products except its standard form of limited warranty ("Limited Warranty") per the terms and conditions of the congatec entity, which the product is delivered from. These terms and conditions can be downloaded from www.congatec.com. congatec GmbH may in its sole discretion modify its Limited Warranty at any time and from time to time.

The products may include software. Use of the software is subject to the terms and conditions set out in the respective owner's license agreements, which are available at www.congatec.com and/or upon request.

Beginning on the date of shipment to its direct customer and continuing for the published warranty period, congatec GmbH represents that the products are new and warrants that each product failing to function properly under normal use, due to a defect in materials or workmanship or due to non conformance to the agreed upon specifications, will be repaired or exchanged, at congatec's option and expense.

Customer will obtain a Return Material Authorization ("RMA") number from congatec GmbH prior to returning the non conforming product freight prepaid. congatec GmbH will pay for transporting the repaired or exchanged product to the customer.

Repaired, replaced or exchanged product will be warranted for the repair warranty period in effect as of the date the repaired, exchanged or replaced product is shipped by congatec, or the remainder of the original warranty, whichever is longer. This Limited Warranty extends to congatec's direct customer only and is not assignable or transferable.

Except as set forth in writing in the Limited Warranty, congatec makes no performance representations, warranties, or guarantees, either express or implied, oral or written, with respect to the products, including without limitation any implied warranty (a) of merchantability, (b) of fitness for a particular purpose, or (c) arising from course of performance, course of dealing, or usage of trade.

congatec GmbH shall in no event be liable to the end user for collateral or consequential damages of any kind. congatec shall not otherwise be liable for loss, damage or expense directly or indirectly arising from the use of the product or from any other cause. The sole and exclusive remedy against congatec, whether a claim sound in contract, warranty, tort or any other legal theory, shall be repair or replacement of the product only.

#### Certification

congatec GmbH is certified to DIN EN ISO 9001 standard.

7/65

## **Technical Support**

congatec GmbH technicians and engineers are committed to providing the best possible technical support for our customers so that our products can be easily used and implemented. We request that you first visit our website at www.congatec.com for the latest documentation, utilities and drivers, which have been made available to assist you. If you still require assistance after visiting our website then contact our technical support department by email at support@congatec.com.

## Terminology

| Term                  | Description                                                                                                                                                                                       |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Express (PCIe)    | Peripheral Component Interface Express – next-generation high speed Serialized I/O bus                                                                                                            |

| ARM                   | Advanced RISC Machine                                                                                                                                                                             |

| JTAG                  | Joint Test Action Group                                                                                                                                                                           |

| eCSPI                 | Enhanced Configurable Serial Peripheral Interface                                                                                                                                                 |

| MIPI                  | Mobile Industry CPU Interface                                                                                                                                                                     |

| GPIO                  | General Purpose Input Output                                                                                                                                                                      |

| RGMII                 | Reduced Gigabit Media Independent Interface                                                                                                                                                       |

| PCI Express Lane      | One PCI Express Lane is a set of 4 signals that contains two differential lines for transmitting and two differential lines for Receiving. Clocking information is embedded into the data stream. |

| PCI Express Mini Card | PCI Express Mini Card add-in card is a small size unique form factor optimized for mobile computing platforms.                                                                                    |

| eMMC                  | Embedded Multi Media Card is a non-volatile memory system, which frees the processor from low level flash memory management.                                                                      |

| SDIO card             | SDIO (Secure Digital Input Output) is a non-volatile memory card format developed for use in portable devices.                                                                                    |

| USB                   | Universal Serial Bus                                                                                                                                                                              |

| SATA                  | Serial AT Attachment: serial-interface standard for hard disks                                                                                                                                    |

| HDA                   | High Definition Audio                                                                                                                                                                             |

| HDMI                  | High Definition Multimedia Interface. HDMI supports standard, enhanced, or high-definition video, plus multi-channel digital audio on a single cable.                                             |

| TMDS                  | Transition Minimized Differential Signaling. TMDS is a signaling interface defined by Silicon Image that is used for DVI and HDMI.                                                                |

| DVI                   | Digital Visual Interface is a video interface standard developed by the Digital Display Working Group (DDWG).                                                                                     |

| I <sup>2</sup> C Bus  | Inter-Integrated Circuit Bus: is a simple two-wire bus with a software-defined protocol that was developed to provide the communications link between integrated circuits in a system.            |

| SM Bus                | System Management Bus: is a popular derivative of the I <sup>2</sup> C-bus.                                                                                                                       |

| SPI Bus               | Serial Peripheral Interface is a synchronous serial data link standard named by Motorola that operates in full duplex mode.                                                                       |

| CAN Bus               | Controller-area network is a vehicle bus standard designed to allow microcontrollers and devices to communicate with each other within a vehicle without a host computer.                         |

| AMBA                  | Advanced Microcontroller Bus Architecture                                                                                                                                                         |

| IOMUX                 | Input Output Multiplexer                                                                                                                                                                          |

| GbE                   | Gigabit Ethernet                                                                                                                                                                                  |

| LVDS                  | Low-Voltage Differential Signaling                                                                                                                                                                |

| DDC                   | Display Data Channel is an I <sup>2</sup> C bus interface between a display and a graphics adapter.                                                                                               |

| N.C.                  | Not connected                                                                                                                                                                                     |

| N.A.                  | Not available                                                                                                                                                                                     |

| T.B.D.                | To be determined                                                                                                                                                                                  |

# Contents

|                                                                               | nernet31                                      |

|-------------------------------------------------------------------------------|-----------------------------------------------|

|                                                                               | 21                                            |

| 5.5 USD 0.0                                                                   | 31                                            |

| z. i Fediule List                                                             |                                               |

| 2.2 Supported Operating Systems                                               |                                               |

| 2.5 Weditalical Differsions                                                   | .C'9732                                       |

|                                                                               | 33                                            |

| 2.4.   E CUICA  C  A AUCINICS                                                 | 33                                            |

| Z.4.Z NISE TITLE                                                              | 34                                            |

| 2.3   TOWELCOUSUIDUOL                                                         | 34                                            |

| Z D T TNAC TIMAO COHEX AZ TUCHOZ BIHOHE COHE DIZKOTZ GALHE ZU                 | 34                                            |

|                                                                               | ring/JTAG Interface34                         |

|                                                                               | trol35                                        |

|                                                                               | nagement36                                    |

| Z.J.J IVAI I.IVIAU CUITEX A.Z. I.U CITIZ CUIGU CUIE TIVID LZ CICLIE Z.I       | 37                                            |

| 2.5.6 NXP® i.MX6 Cortex A9 800 MHz Single Core 512kB L2 cache 5.17 I2C Bus    | 37                                            |

| 9                                                                             | Features38                                    |

| 0. F.7 NVD®: MV/ Contact AO 000 MH = Decel 1:to F12kD 1.2 contact (2CD)       |                                               |

| eMMC)                                                                         | ance Boot (HAB)                               |

| / 5 X                                                                         | Hardware Accelerators                         |

| eMMC) 22 6.3 Power Man                                                        | nagement38                                    |

| 2.5.9 NXP® i.MX6 Cortex A9 800 MHz Quad Core 1MB L2 cache (2GB 6.4 Dynamic Vo | oltage and Frequency Scaling                  |

| oMMC) 22 6.5 Smart Spee                                                       | ed Technology                                 |

| 2.5.10 NXP® i.MX6 Cortex A9 800 MHz Quad Core 1MB L2 cache (4GB 6.6 Suspend M | lode39                                        |

|                                                                               | nologies40                                    |

|                                                                               | cessing Engine (MPE-NEON)40                   |

| 2/1 CMOC Detter Dever Comment of                                              | X                                             |

| 7.2 Jazelle DD/                                                               | ^40<br>40                                     |

|                                                                               | oint Unit                                     |

| 4 Hastonroader 27 8 conga Tech                                                | n Notes41                                     |

| Treatspreader20                                                               |                                               |

|                                                                               | 6 Processor Features41 re Monitor (TEMPMON)41 |

|                                                                               | anagement41                                   |

|                                                                               | 42                                            |

| .4<br>.5   | LVDS BridgeUSB Port Connections                   |    |

|------------|---------------------------------------------------|----|

| 1          | Interface - Signal Descriptions and Pinout Tables | 44 |

| .1         | Bootstrap Signals                                 | 60 |

| 0          | Onboard Interfaces and Devices                    | 61 |

| 0.1<br>0.2 | UART/RS-232 Debug PortMIPI/CMOS Camera            |    |

| 0.2        | JTAG Interface                                    | 64 |

| 0.4        | SPI Flash                                         | 64 |

| 0.5        | Android Buttons                                   | 65 |

| 0.6        | DDR3L Memory                                      | 65 |

| 0.7        | eMMC                                              |    |

| 0.8        | Micro SD                                          |    |

# List of Tables

| Table 1  | Commercial variants                    | 13 |

|----------|----------------------------------------|----|

| Table 2  | Industrial Variants                    |    |

| Table 3  | Commercial Variants                    | 14 |

| Table 4  | Industrial Variants                    | 14 |

| Table 5  | Commercial Variants                    | 15 |

| Table 6  | Industrial Variants                    | 15 |

| Table 7  | Feature Summary                        | 16 |

| Table 8  | Cooling Solution Variants              | 26 |

| Table 9  | Signal Tables Terminology Descriptions | 44 |

| Table 10 | Edge Finger Pinout                     |    |

| Table 11 | PCI Express Signal Descriptions        | 48 |

| Table 12 | UART Signal Descriptions               |    |

| Table 13 | Ethernet Signal Descriptions           | 49 |

| Table 14 | SATA Signal Descriptions               |    |

| Table 15 | USB 2.0 Signal Descriptions            |    |

| Table 16 | SDIO/MMC Signal Descriptions           |    |

| Table 17 | HDA/I2S/SPDIF Signal Descriptions      | 52 |

| Table 18 | LVDS Signal Descriptions               |    |

| Table 19 | DisplayPort Signal Descriptions        | 54 |

| Table 20 | HDMI® Signal Descriptions              |    |

| Table 21 | LPC/GPIO Signal Descriptions           |    |

| Table 22 | SPI Interface Signal Descriptions      | 55 |

| Table 23 | CAN Bus Signal Descriptions            |    |

| Table 24 | Input Power Signal Descriptions        |    |

| Table 25 | Power Control Signal Descriptions      | 56 |

| Table 26 | Power Management Signal Descriptions   | 57 |

| Table 27 | Miscellaneous Signal Descriptions      | 57 |

| Table 28 | Manufacturing/JTAG Signal Descriptions |    |

| Table 29 | Thermal Management Signal Descriptions |    |

| Table 30 | Fan Control Signal Descriptions        | 59 |

| Table 31 | Bootstrap Signal Descriptions          |    |

| Table 32 | UART Signal Descriptions               | 61 |

| Table 33 | MIPI Signal Descriptions               |    |

| Table 34 | JTAG Interface Signal Descriptions     |    |

| Table 35 | Android Button Signal Descriptions     | 65 |

|          | ·                                      |    |

## 1 INTRODUCTION

## Oseven® Concept

The Qseven® concept is an off-the-shelf, multi vendor, Computer-On-Module that integrates all the core components of a common PC and is mounted onto an application specific carrier board. Qseven® modules have a standardized form factor of 70mm x 70mm and a specified pinout based on the high speed MXM system connector. The pinout remains the same regardless of the vendor. The Qseven® module provides the functional requirements for an embedded application. These functions include, but are not limited to, graphics, sound, mass storage, network interface and multiple USB ports.

A single ruggedized MXM connector provides the carrier board interface to carry all the I/O signals to and from the Qseven® module. This MXM connector is a well known and proven high speed signal interface connector that is commonly used for high speed PCI Express® graphics cards in notebooks.

Carrier board designers can use as little or as many of the I/O interfaces as deemed necessary. The carrier board can therefore provide all the interface connectors required to attach the system to the application specific peripherals. This versatility allows the designer to create a dense and optimized package, which results in a more reliable product while simplifying system integration.

The conga-QEVAL/Qseven® 2.0 evaluation carrier board provides carrier board designers with a reference design platform and the opportunity to test all the Qseven® I/O interfaces available and then choose what are suitable for their application. Qseven® applications are scalable, which means once a carrier board has been created there is the ability to diversify the product range through the use of different performance class Qseven® modules. Simply unplug one module and replace it with another, no need to redesign the carrier board.

The conga-QMX6 B.x and later revisions are designed based on the Qseven Specification 2.0. Revision C.x follows the Qseven Specification 2.0 Errata. Revision E.x follows the Qseven Specification 2.1.

## conga-QMX6 Options Information (Revision B.x)

The conga-QMX6 revision B.x was available in eleven variants (seven commercial and four industrial). Below you will find an order table showing the base configuration modules that were offered by congatec GmbH. The part numbers are obsolete as of revision C.x. For more information about additional conga-QMX6 variants offered by congatec, contact your local congatec sales representative or visit the congatec website at www.congatec.com.

Table 1 Commercial variants

| Part-No.         | 016100            | 016101            | 016102        | 016103            | 016104            | 016105            | 016106            |

|------------------|-------------------|-------------------|---------------|-------------------|-------------------|-------------------|-------------------|

| Processor        | NXP® i.MX6        | NXP® i.MX6        | NXP® i.MX6    | NXP® i.MX6        | NXP® i.MX6        | NXP® i.MX6        | NXP® i.MX6        |

|                  | Cortex A9 1.0 GHz | Cortex A9 1.0 GHz | Cortex A9 1.0 | Cortex A9 1.0 GHz |

|                  | Single Core       | Dual Lite         | GHz Dual Core | Quad Core         | Quad Core         | Quad Core         | Quad Core         |

| L2 Cache         | 512 kB            | 512 kB            | 1 MB          | 1 MB              | 1 MB              | 1 MB              | 1 MB              |

| Onboard Memory   | 1GB DDR3L         | 1GB DDR3L         | 1GB DDR3L     | 1GB DDR3L         | 2GB DDR3L         | 2GB DDR3L         | 1GB DDR3L         |

| eMMC up to 8GB   | 4GB               | 4GB               | 4GB           | 4GB               | 4GB               | 8GB               | 8GB               |

| PCI Express Lane | Yes               | Yes               | Yes           | Yes               | Yes               | Yes               | Yes               |

| CAN Bus          | Yes               | Yes               | Yes           | Yes               | Yes               | Yes               | Yes               |

| Gigabit Ethernet | Yes               | Yes               | Yes           | Yes               | Yes               | Yes               | Yes               |

| SATA             | No                | No                | Yes           | Yes               | Yes               | Yes               | Yes               |

Table 2 Industrial Variants

| Part-No.         | 016110            | 016111            | 016112            | 016113            |

|------------------|-------------------|-------------------|-------------------|-------------------|

| Processor        | NXP® i.MX6        | NXP® i.MX6        | NXP® i.MX6        | NXP® i.MX6        |

|                  | Cortex A9 800 MHz |

|                  | Single Core       | Dual Lite         | Dual Core         | Quad Core         |

| L2 Cache         | 512 kB            | 512 kB            | 1 MB              | 1 MB              |

| Onboard Memory   | 1GB DDR3L         | 1GB DDR3L         | 1GB DDR3L         | 1GB DDR3L         |

| eMMC up to 8GB   | 4GB               | 4GB               | 4GB               | 4GB               |

| PCI Express Lane | Yes               | Yes               | Yes               | Yes               |

| CAN Bus          | Yes               | Yes               | Yes               | Yes               |

| Gigabit Ethernet | Yes               | Yes               | Yes               | Yes               |

| SATA             | No                | No                | Yes               | Yes               |

Caution

Do not alter the conga-QMX6 boot fuse settings. These fuse settings are already programmed during production process and are not protected against alteration. Changing the boot fuse settings will void the congatec GmbH warranty.

## conga-QMX6 Options Information (Revision C.x)

Revision C.x of the conga-QMX6 was available in twelve variants (seven commercial and five industrial). Below you will find an order table showing the base configuration modules that were offered by congatec GmbH. For more information about additional conga-QMX6 variants offered by congatec, contact your local congatec sales representative or visit the congatec website at www.congatec.com.

Table 3 Commercial Variants

| Part-No.         | 016300            | 016301            | 016302            | 016303            | 016304            | 016305            | 016306            |

|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Processor        | NXP® i.MX6        |

|                  | Cortex A9 1.0 GHz |

|                  | Single Core       | Dual Lite         | Dual Core         | Quad Core         | Quad Core         | Quad Core         | Quad Core         |

| L2 Cache         | 512 kB            | 512 kB            | 1 MB              |

| Onboard Memory   | 1GB DDR3L         | 1GB DDR3L         | 1GB DDR3L         | 1GB DDR3L         | 2GB DDR3L         | 2GB DDR3L         | 1GB DDR3L         |

| eMMC up to 8GB   | 4GB               | 4GB               | 4GB               | 4GB               | 4GB               | 8GB               | 8GB               |

| PCI Express Lane | Yes               |

| CAN Bus          | Yes               |

| Gigabit Ethernet | Yes               |

| SATA             | No                | No                | Yes               | Yes               | Yes               | Yes               | Yes               |

Table 4 Industrial Variants

| Part-No.         | 016310            | 016311            | 016312            | 016313            | 016318            |

|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Processor        | NXP® i.MX6        |

|                  | Cortex A9 800 MHz |

|                  | Single Core       | Dual Lite         | Dual Core         | Quad Core         | Quad Core         |

| L2 Cache         | 512 kB            | 512 kB            | 1 MB              | 1 MB              | 1 MB              |

| Onboard Memory   | 1GB DDR3L         | 1GB DDR3L         | 1GB DDR3L         | 1GB DDR3L         | 4GB DDR3L         |

| eMMC up to 8GB   | 4GB               | 4GB               | 4GB               | 4GB               | 4GB               |

| PCI Express Lane | Yes               | Yes               | Yes               | Yes               | Yes               |

| CAN Bus          | Yes               | Yes               | Yes               | Yes               | Yes               |

| Gigabit Ethernet | Yes               | Yes               | Yes               | Yes               | Yes               |

| SATA             | No                | No                | Yes               | Yes               | Yes               |

#### Caution

Do not alter the conga-QMX6 boot fuse settings. These fuse settings are already programmed during production process and are not protected against alteration. Changing the boot fuse settings will void the congatec GmbH warranty.

## conga-QMX6 Options Information (Revision E.x)

Revision E.x of the conga-QMX6 is currently available in ten variants (five commercial and five industrial). Below you will find an order table showing the base configuration modules that are currently offered by congatec GmbH. For more information about additional conga-QMX6 variants offered by congatec, contact your local congatec sales representative or visit the congatec website at www.congatec.com.

Table 5 Commercial Variants

| Part-No.         | 016300               | 016301               | 016302               | 016303               | 016304               |

|------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Processor        | NXP® i.MX6 Cortex A9 |

|                  | 1.0 GHz Single Core  | 1.0 GHz Dual Lite    | 1.0 GHz Dual Core    | 1.0 GHz Quad Core    | 1.0 GHz Quad Core    |

| L2 Cache         | 512 kB               | 512 kB               | 1 MB                 | 1 MB                 | 1 MB                 |

| Onboard Memory   | 1GB DDR3L            | 1GB DDR3L            | 1GB DDR3L            | 1GB DDR3L            | 2GB DDR3L            |

| eMMC             | 32GB                 | 32GB                 | 32GB                 | 32GB                 | 32GB                 |

| PCI Express Lane | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| CAN Bus          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Gigabit Ethernet | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| SATA             | No                   | No                   | Yes                  | Yes                  | Yes                  |

Table 6 Industrial Variants

| Part-No.         | 016310               | 016311               | 016312               | 016313               | 016318               |

|------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Processor        | NXP® i.MX6 Cortex A9 |

|                  | 800 MHz Single Core  | 800 MHz Dual Lite    | 800 MHz Dual Core    | 800 MHz Quad Core    | 800 MHz Quad Core    |

| L2 Cache         | 512 kB               | 512 kB               | 1 MB                 | 1 MB                 | 1 MB                 |

| Onboard Memory   | 1GB DDR3L            | 1GB DDR3L            | 1GB DDR3L            | 1GB DDR3L            | 4GB DDR3L            |

| eMMC             | 32GB                 | 32GB                 | 32GB                 | 32GB                 | 32GB                 |

| PCI Express Lane | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| CAN Bus          | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| Gigabit Ethernet | Yes                  | Yes                  | Yes                  | Yes                  | Yes                  |

| SATA             | No                   | No                   | Yes                  | Yes                  | Yes                  |

#### Caution

Do not alter the conga-QMX6 boot fuse settings. These fuse settings are already programmed during production process and are not protected against alteration. Changing the boot fuse settings will void the congatec GmbH warranty.

# 2 Specifications

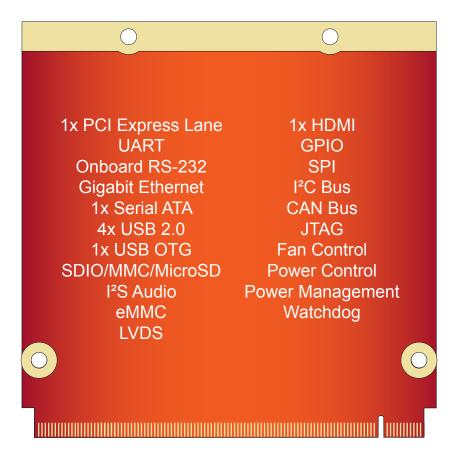

#### 2.1 Feature List

Table 7 Feature Summary

| Form Factor       | Qseven   70x70mm                                                                                                                                                                                                |                                                                                              |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|

| Processor         | NXP® i.MX6 Cortex A9                                                                                                                                                                                            |                                                                                              |  |  |  |

| DRAM              | Up to 4 GByte onboard DDR3L memory                                                                                                                                                                              | 1066 MT/s                                                                                    |  |  |  |

| Ethernet          | 1x Gbit Ethernet                                                                                                                                                                                                |                                                                                              |  |  |  |

| I/O Interfaces    | 5x USB 2.0 (shared with 1x USB OTG clie                                                                                                                                                                         | nt)   SATA (only i.MX6 Dual/Quad)   1x SDIO   1x PCIe   I <sup>2</sup> C Bus   CAN Bus   SPI |  |  |  |

| Mass Storage      | eMMC up to 32 GByte   Onboard MicroS                                                                                                                                                                            | D socket                                                                                     |  |  |  |

| Sound             | 1x I <sup>2</sup> S                                                                                                                                                                                             |                                                                                              |  |  |  |

| Graphics          | Integrated in NXP i.MX6   Video (VPU)   2D Graphics (GPU2D) and 3D Graphics (GPU3D)   3D graphics with 4 shaders up to 200MT/s dual stream 1080p/720p decoder/encoder   OpenGL   OpenCL   OpenVG 1.1            |                                                                                              |  |  |  |

| Video Interfaces  | HDMI v1.4 support supported by Qseven specification.2x LVDS (2x 24 bit)   1x LVDS (1x 24 bit) up to WUXGA resolution   1920x1200 pixel and HD1080   Supports 18bit and 24bit dual channel up to WUXGA 1920x1200 |                                                                                              |  |  |  |

| Features          | Watchdog Timer   JTAG debug interface   MIPI CSI-2 camera interface on flat foil connector   High Precision Real Time Clock                                                                                     |                                                                                              |  |  |  |

| Security          | High Assurance Boot support   TrustZone                                                                                                                                                                         | ®   RNG                                                                                      |  |  |  |

| Boot Loader       | U-Boot boot loader                                                                                                                                                                                              |                                                                                              |  |  |  |

| Operating Systems | Linux   Android                                                                                                                                                                                                 |                                                                                              |  |  |  |

| Power             | Typical application 3-5W @ 5V                                                                                                                                                                                   |                                                                                              |  |  |  |

| Consumption       |                                                                                                                                                                                                                 |                                                                                              |  |  |  |

| Temperature       |                                                                                                                                                                                                                 | o +60°C commercial grade                                                                     |  |  |  |

| Range             |                                                                                                                                                                                                                 | 0 to +85°C industrial grade<br>0 to +85°C                                                    |  |  |  |

| Humidty           | Operating: 10 - 90% r. H. non cond. Sto                                                                                                                                                                         | orage: 5 - 95% r. H. non cond.                                                               |  |  |  |

Some of the features mentioned in the above feature summary are optional. Check the article number of your module and compare it to the conga-QMX6 options information list on page 12 of this user's guide to determine what options are available on your particular module.

## 2.2 Supported Operating Systems

The conga-QMX6 supports the following operating systems.

- Android

- Linux

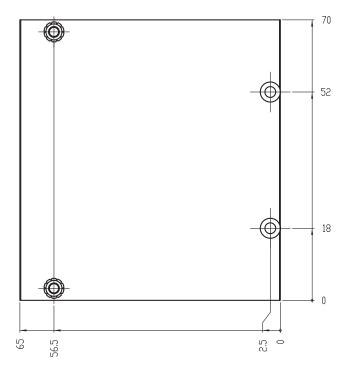

### 2.3 Mechanical Dimensions

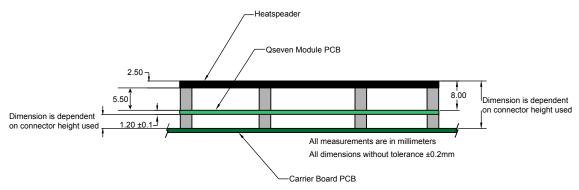

- 70.0 mm x 70.0 mm @ (2 ¾" x 2 ¾")

- The Qseven™ module, including the heatspreader plate, PCB thickness and bottom components, is up to approximately 12mm thick.

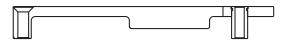

Rear View of Qseven Module

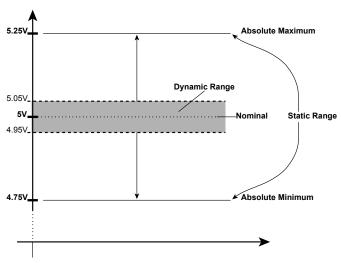

## 2.4 Supply Voltage Standard Power

• 5V DC ± 5%

The dynamic range shall not exceed the static range.

#### 2.4.1 Electrical Characteristics

| <b>Characteristics</b> |         |      | Min. | Тур. | Max. | Units            | Comment |

|------------------------|---------|------|------|------|------|------------------|---------|

| 5V                     | Voltage | ± 5% | 4.75 | 5.00 | 5.25 | Vdc              |         |

|                        | Ripple  |      | -    | -    | ± 50 | mV <sub>PP</sub> | 0-20MHz |

|                        | Current |      |      |      |      |                  |         |

| 5V_SB                  | Voltage | ± 5% | 4.75 | 5.00 | 5.25 | Vdc              |         |

|                        | Ripple  |      |      |      | ± 50 | mV <sub>PP</sub> |         |

#### 2.4.2 Rise Time

The input voltages shall rise from 10% of nominal to 90% of nominal at a minimum slope of 250V/s. The smooth turn-on requires that during the 10% to 90% portion of the rise time, the slope of the turn-on waveform must be positive.

For information about the input power sequencing of the Qseven® module, refer to the Qseven® specification.

## 2.5 Power Consumption

The power consumption values listed in this section were measured under a controlled environment. The hardware used for testing includes a conga-QMX6 module, carrier board for Qseven ARM, TFT monitor, micro-SD card and USB keyboard. The carrier board was powered externally by a power supply unit so that it does not influence the power consumption value that is measured for the module. The USB keyboard was detached once the module was configured within the OS. All recorded values were averaged over a 30 second time period. The modules were cooled by the heatspreader specific to the module variants

Each module was measured while running 32 bit Linaro Ubuntu 11.10. To measure the worst case power consumption, the cooling solution was removed and the CPU core temperature was allowed to run between 95° and 100°C at 100% workload. The peak current value was then recorded. This value should be taken into consideration when designing the system's power supply to ensure that the power supply is sufficient during worst case scenarios.

Power consumption values were recorded during the following stages:

Linaro Ubuntu 11.10 (32 bit)

- Desktop Idle

- 100% CPU workload

- 100% CPU workload at approximately 100°C peak power consumption

With the Linux stress tool, we stressed the CPU to maximum frequency.

#### **Processor Information**

The tables below provide additional information about the different variants offered by the conga-QMX6.

## 2.5.1 NXP® i.MX6 Cortex A9 1.0 GHz Single Core 512kB L2 cache

With 4GB onboard eMMC

| conga-QMX6 Art. No. 016100 / 016300         | NXP® i.MX6 Cortex A9 1.0 GHz 512kB L2 cache (40nm) |                |                        |

|---------------------------------------------|----------------------------------------------------|----------------|------------------------|

| Memory Size                                 | 1GB onboard                                        |                |                        |

| Operating System                            | Ubuntu                                             |                |                        |

| Power State                                 | Desktop Idle                                       | 100% workload  | Max. Power Consumption |

| Power consumption (measured in Ampere/Watt) | 0.22 A / 1.1 W                                     | 0.34 A / 1.7 W | 0.46 A /2.3 W          |

#### 2.5.2 NXP® i.MX6 Cortex A9 1.0 GHz Dual Lite 512kB L2 cache

With 4GB onboard eMMC

| conga-QMX6 Art. No. 016101 / 016301         | NXP® i.MX6 Cortex A9 1.0 GHz 512kB L2 cache (40nm) |                |                        |  |

|---------------------------------------------|----------------------------------------------------|----------------|------------------------|--|

| Memory Size                                 | 1GB onboard                                        |                |                        |  |

| Operating System                            | Ubuntu                                             |                |                        |  |

| Power State                                 | Desktop Idle                                       | 100% workload  | Max. Power Consumption |  |

| Power consumption (measured in Ampere/Watt) | 0.26 A / 1.3 W                                     | 0.44 A / 2.2 W | 0.66 A / 3.3 W         |  |

### 2.5.3 NXP® i.MX6 Cortex A9 1.0 GHz Dual Core 1MB L2 cache

With 4GB onboard eMMC

| conga-QMX6 Art. No. 016102 / 016302         | NXP® i.MX6 Cortex A9 1.0 GHz 1MB L2 cache (40nm) |               |                        |

|---------------------------------------------|--------------------------------------------------|---------------|------------------------|

| Memory Size                                 | 1GB onboard                                      |               |                        |

| Operating System                            | Ubuntu                                           |               |                        |

| Power State                                 | Desktop Idle                                     | 100% workload | Max. Power Consumption |

| Power consumption (measured in Ampere/Watt) | 0.28 A / 1.4 W                                   | 0.5 A / 2.5 W | 0.7 A / 3.2 W          |

#### 2.5.4 NXP® i.MX6 Cortex A9 1.0 GHz Quad Core 1MB L2 cache

#### With 4GB onboard eMMC

| conga-QMX6 Art. No. 016103 / 016303         | NXP® i.MX6 Cortex A9 1.0 GHz 1MB L2 cache (40nm) |                |                        |

|---------------------------------------------|--------------------------------------------------|----------------|------------------------|

| Memory Size                                 | 1GB onboard                                      |                |                        |

| Operating System                            | Ubuntu                                           |                |                        |

| Power State                                 | Desktop Idle                                     | 100% workload  | Max. Power Consumption |

| Power consumption (measured in Ampere/Watt) | 0.3 A / 1.5 W                                    | 0.72 A / 3.6 W | 0.92 A / 4.6 W         |

#### 2.5.5 NXP® i.MX6 Cortex A9 1.0 GHz Quad Core 1MB L2 cache

#### With 4GB onboard eMMC

| conga-QMX6 Art. No. 016104 / 016304         | NXP® i.MX6 Cortex A9 1.0 GHz 1MB L2 cache (40nm) |                |                        |

|---------------------------------------------|--------------------------------------------------|----------------|------------------------|

| Memory Size                                 | 2GB onboard                                      |                |                        |

| Operating System                            | Ubuntu                                           |                |                        |

| Power State                                 | Desktop Idle                                     | 100% workload  | Max. Power Consumption |

| Power consumption (measured in Ampere/Watt) | 0.3 A / 1.5 W                                    | 0.74 A / 3.7 W | 0.94 A / 4.7 W         |

## 2.5.6 NXP® i.MX6 Cortex A9 800 MHz Single Core 512kB L2 cache (2GB eMMC)

#### With 2GB onboard eMMC

| conga-QMX6 Art. No. 016110 / 016310         | NXP® i.MX6 Cortex A9 800 MHz 512kB L2 cache (40nm) |                |                        |

|---------------------------------------------|----------------------------------------------------|----------------|------------------------|

| Memory Size                                 | 1GB onboard                                        |                |                        |

| Operating System                            | Ubuntu                                             |                |                        |

| Power State                                 | Desktop Idle                                       | 100% workload  | Max. Power Consumption |

| Power consumption (measured in Ampere/Watt) | 0.24 A / 1.2 W                                     | 0.30 A / 1.5 W | 0.48 A / 2.1 W         |

## 2.5.7 NXP® i.MX6 Cortex A9 800 MHz Dual Lite 512kB L2 cache (2GB eMMC)

#### With 2GB onboard eMMC

| conga-QMX6 Art. No. 016111 / 016311         | NXP® i.MX6 Cortex A9 800 MHz 512kB L2 cache (40nm) |               |                        |  |

|---------------------------------------------|----------------------------------------------------|---------------|------------------------|--|

| Memory Size                                 | 1GB onboard                                        |               |                        |  |

| Operating System                            | Ubuntu                                             |               |                        |  |

| Power State                                 | Desktop Idle                                       | 100% workload | Max. Power Consumption |  |

| Power consumption (measured in Ampere/Watt) | TBD A / W                                          | TBD A / W     | TBD A / W              |  |

### 2.5.8 NXP® i.MX6 Cortex A9 800 MHz Dual Core 1MB L2 cache (2GB eMMC)

#### With 2GB onboard eMMC

| conga-QMX6 Art. No. 016112 / 016312         | NXP® i.MX6 Cortex A9 800 MHz 1MB L2 cache (40nm) |                |                        |  |

|---------------------------------------------|--------------------------------------------------|----------------|------------------------|--|

| Memory Size                                 | 1GB onboard                                      |                |                        |  |

| Operating System                            | Ubuntu                                           |                |                        |  |

| Power State                                 | Desktop Idle                                     | 100% workload  | Max. Power Consumption |  |

| Power consumption (measured in Ampere/Watt) | 0.30 A / 1.5W                                    | 0.42 A / 2.1 W | 0.60 A / 3.0 W         |  |

## 2.5.9 NXP® i.MX6 Cortex A9 800 MHz Quad Core 1MB L2 cache (2GB eMMC)

#### With 2GB onboard eMMC

| conga-QMX6 Art. No. 016113 / 016313         | NXP® i.MX6 Cortex A9 800 MHz 1MB L2 cache (40nm) |                |                        |  |

|---------------------------------------------|--------------------------------------------------|----------------|------------------------|--|

| Memory Size                                 | 1GB onboard                                      |                |                        |  |

| Operating System                            | Ubuntu                                           |                |                        |  |

| Power State                                 | Desktop Idle                                     | 100% workload  | Max. Power Consumption |  |

| Power consumption (measured in Ampere/Watt) | 0.30 A / 1.5 W                                   | 0.54 A / 2.7 W | 0.72 A / 3.6 W         |  |

### 2.5.10 NXP® i.MX6 Cortex A9 800 MHz Quad Core 1MB L2 cache (4GB eMMC)

#### With 4GB onboard eMMC

| conga-QMX6 Art. No. 016318                  | NXP® i.MX6 Cortex A9 800 MHz 1MB L2 cache (40nm) |               |                        |  |

|---------------------------------------------|--------------------------------------------------|---------------|------------------------|--|

| Memory Size                                 | 4GB onboard                                      |               |                        |  |

| Operating System                            | Ubuntu                                           |               |                        |  |

| Power State                                 | Desktop Idle                                     | 100% workload | Max. Power Consumption |  |

| Power consumption (measured in Ampere/Watt) | TBD A/ W                                         | TBD A/ W      | TBD A/ W               |  |

All recorded power consumption values are approximate and only valid for the controlled environment described earlier. 100% workload refers to the CPU workload and not the maximum workload of the complete module. Power consumption results will vary depending on the workload of other components such as graphics engine, memory, etc.

## 2.6 Supply Voltage Battery Power

- 2.0V-3.6V DC

- Typical 3V DC

## 2.6.1 CMOS Battery Power Consumption

| RTC @ 20°C                        | Voltage | Current |

|-----------------------------------|---------|---------|

| RTC onboard the conga-QMX6 module | 3V DC   | 1.45 μΑ |

The CMOS battery power consumption value listed above should not be used to calculate CMOS battery lifetime. You should measure the CMOS battery power consumption in your customer specific application in worst case conditions, for example during high temperature and high battery voltage. The self-discharge of the battery must also be considered when determining CMOS battery lifetime. For more information about calculating CMOS battery lifetime refer to application note AN9\_RTC\_Battery\_Lifetime.pdf, which can be found on the congatec GmbH website at www.congatec.com.

To improve the lifetime of the CMOS battery, congatec implemented an external real-time clock onboard the conga-QMX6 module.

## 2.7 Environmental Specifications

Temperature Operation: 0° to 60°C Storage: -40° to +85°C (commercial grade variants of conga-QMX6)

Temperature Operation: -40° to 85°C Storage: -40° to +85°C (industrial grade variants of conga-QMX6)

Humidity Operation: 10% to 90% Storage: 5% to 95% (humidity specifications are for non-condensing conditions)

#### Caution

The above operating temperatures must be strictly adhered to at all times.

For long term storage of the conga-QMX6 (more than six months), keep the conga-QMX6 in a climate-controlled building at a constant temperature between 5°C and 40°C, with humidity of less than 65% and at an altitude of less than 3000 m. Also ensure the storage location is dry and well ventilated.

We do not recommend storing the conga-QMX6 for more than five years under these conditions.

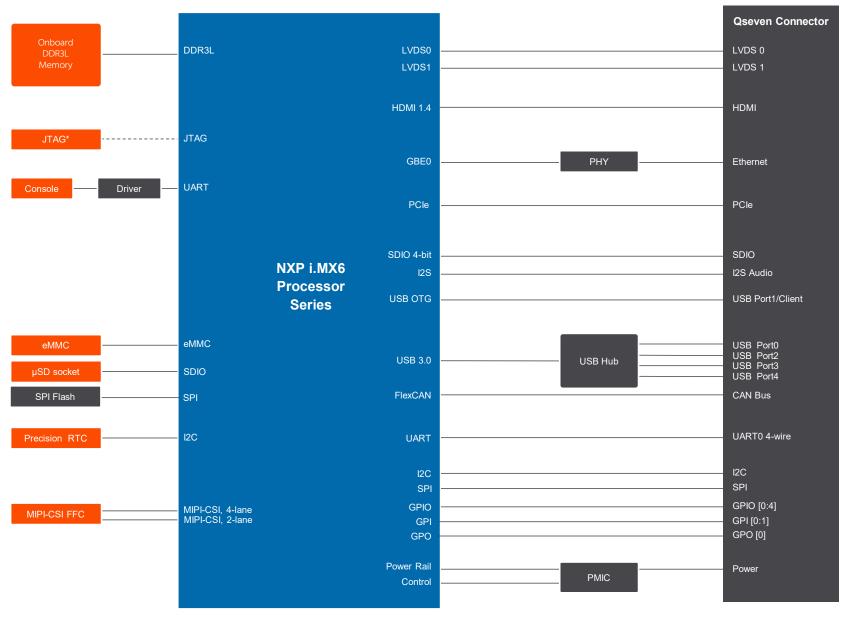

# 3 Block Diagram

<sup>\*</sup> Assembly Option

Copyright © 2013 congatec GmbH QMX6m14 25/65

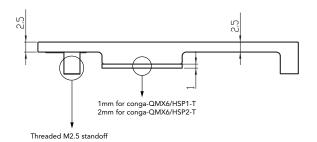

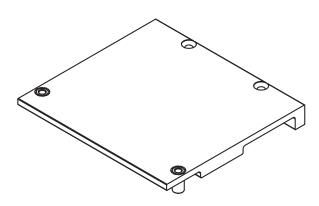

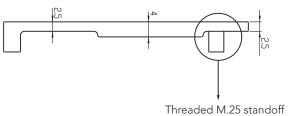

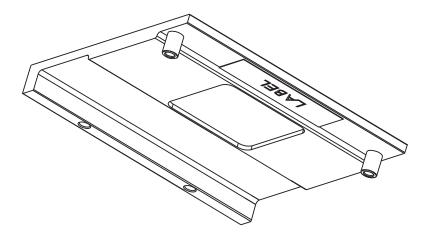

## 4 Heatspreader

congatec GmbH offers three heatspreader variants for the conga-QMX6. Each heatspreader variant is intended for specific conga-QMX6 modules as shown in the table below. The dimensions of the cooling solutions are shown in the sub-sections. All measurements are in millimeters.

Table 8 Cooling Solution Variants

| Heatspreader      | Heatspreader  | Compatible conga-QMX6 Variants         | Comment                                                               |

|-------------------|---------------|----------------------------------------|-----------------------------------------------------------------------|

| Variant           | Part No. (PN) | (PN)                                   |                                                                       |

| conga-QMX6/HSP1-T | 016160        | 016112, 016113, 016312, 016313, 016318 | For modules equipped with lidded FC-PBGA CPU (1mm Gap Pad)            |

| conga-QMX6/HSP2-T | 016161        | 016100, 016101, 016110, 016111         | For modules equipped with MA-PBGA CPU (2mm Gap Pad)                   |

|                   |               | 016300, 016301, 016310, 016311         |                                                                       |

| conga-QMX6/HSP3-T | 016162        | 016102, 016103, 016104, 016105, 016106 | For modules equipped with non-lidded FC-PBGA CPU (heatstack solution) |

| _                 |               | 016302, 016303, 016304, 016305, 016306 |                                                                       |

- 1. We recommend a maximum torque of 0.4 Nm for the mounting screws and to start with the two screws furthest from the CPU die.

- 2. The gap pad material used on congatec heatspreaders may contain silicon oil that can seep out over time depending on the environmental conditions it is subjected to. For more information about this subject, contact your local congatec sales representative and request the gap pad material manufacturer's specification.

- 3. Only a few NXP® iMX6 on-chip devices are enabled by default in the bootloader. With this default configuration, the conga-QMX6 power consumption is low. However, power consumption may increase significantly depending on your application and the workload of the CPU.

- 4. For optimal thermal dissipation, do not store the congatec cooling solutions for more than six months.

#### Caution

- 1. The congatec heatspreaders/cooling solutions are tested only within the commercial temperature range of 0° to 60°C. Therefore, if your application that features a congatec heatspreader/cooling solution operates outside this temperature range, ensure the correct operating temperature of the module is maintained at all times. This may require additional cooling components for your final application's thermal solution.

- 2. For adequate heat dissipation, use the mounting holes on the cooling solution to attach it to the module. Apply thread-locking fluid on the screws if the cooling solution is used in a high shock and/or vibration environment. To prevent the standoff from stripping or cross-threading, use non-threaded carrier board standoffs to mount threaded cooling solutions.

- 3. For applications that require vertically-mounted cooling solution, use only coolers that secure the thermal stacks with fixing post. Without the fixing post feature, the thermal stacks may move.

- 4. When using the heatspreader in a high shock and/or vibration environment, congatec recommends the use of a thread-locking fluid on the heatspreader screws to ensure the above mentioned torque specification is maintained.

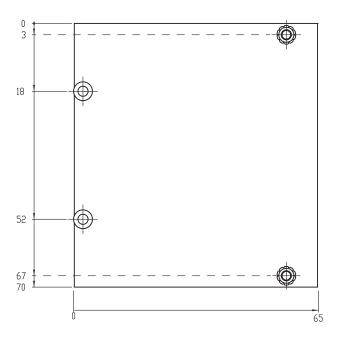

## 4.1 Heatspreader Dimensions

## conga-QMX6/HSP1-T and HSP2-T

## conga-QMX6/HSP3-T

## 5 Connector Subsystems

The conga-QMX6 is based on the Qseven® standard and therefore has 115 edge fingers on the top and bottom side of the module that mate with the 230-pin card-edge MXM connector located on the carrier board. This connector provides the ability to interface the available signals of the conga-QMX6 with the carrier board peripherals.

## 5.1 PCI Express

The conga-QMX6 offers one PCI Express lane. The PCIe signals are routed from the NXP® i.MX6 SoC to the PCI Express port 0 of the conga-QMX6 edge finger. The clock from the SoC imits the speed of the PCI Express interface to Gen 1. Only x1 PCI Express link configuration is possible.

For more information about the PCI Express interface on the edge finger, refer to Table 11.

#### 5.2 UART/RS-232

The conga-QMX6 offers one UART interface on the MXM connector and two RS-232 interfaces onboard. The UART offered on the MXM connector is fully featured with control signals (4 pin UART) and is connected directly to UART3 port of the NXP® i.MX6 Cortex A9 processor.

The conga-QMX6 offers the two onboard RS-232 interfaces via a 6-pin Molex connector. This connector is provided by routing the UART2 and UART5 pins of the NXP® i.MX6 processor to the MAXIM-3232 transceiver. The transceiver converts the Qseven® UART CMOS level (3.3V) to RS-232 voltage levels (5v) and is guaranteed to run at data rates of 250 kbps in the normal operating mode, while maintaining RS-232 output levels. With the Molex connector, you can output data to the console by using the appropriate RS-232 adapter cable.

The UART interfaces support speeds up to 4.0 Mbps and Non-Return-To-Zero encording format, RS-485 compatible 9 bit data format and IrDA compatible infrared slow data rate format.

You can realize a second UART interface on the MFG interface. This implementation however requires a customized conga-QMX6 variant. Contact congatec support for more information.

To display the u-boot output to console, you need an RS-232 adapter cable (PN: 48000023). See section 10.1 "UART/RS-232 Debug Port" for more information about the RS-232 adapter cable and the UART pin description.

#### Caution

The MFG\_NC4 pin is high active on the conga-QMX6 module. This means that the MFG interface on the edge connector functions as JTAG interface by default. Therefore, do not use the MFG interface for UART purposes or externally pull the MFG\_NC4 pin to ground. Failure to adhere to this warning may result to back-driving which can damage the module.

If you need the UART function on the MFG interface, then you require a customized conga-QMX6. For more information, contact congatec support.

## 5.3 Gigabit Ethernet

The conga-QMX6 revision E.x offers Gigabit Ethernet with the integration of Texas Instruments DP83867. This transceiver is implemented via the RGMII interface of the i.MX6 processor. The Ethernet interface consists of 4 pairs of low voltage differential pair signals designated from GBE0\_MDI0± to GBE0\_MDI3± plus control signals for link activity indicators. These signals can be used to connect to a 10/100/1000 BaseT RJ45 connector with integrated or external isolation magnetics on the carrier board.

The conga-QMX6 revision C.x and B.x offer Gigabit Ethernet with the integration of Qualcomm Atheros Gigabit Transceiver. Earlier revisions offer Gigabit Ethernet with the integration of Micrel KSZ 9031 Ethernet PHY.

The theoretical maximum performance of 1 Gbps Ethernet is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For more information, consult NXP's Errata ERR004512.

Some signals have special functionality during the reset process. They may bootstrap some basic important functions of the module. For more information, refer to section 9.1 "Bootstrap Signals" of this user's guide.

#### 5.4 SATA

The NXP® i.MX6 Cortex A9 processor on the conga-QMX6 supports one SATA port only. The supported signals are coupled with 10nF capacitors and then routed to conga-QMX6 edge finger. The conga-QMX6 offers this SATA port on the MXM connector. This port supports SATA I (1.5Gbps) and SATA II (3Gbps) and is compliant with SATA specification 3.0, AHCI specification 1.3 and Advanced Microcontroller Bus Architecture (AMBA) specification 2.0.

SATA interface is only supported on conga-QMX6 quad and dual core variants. Solo core and dual lite variants do not support SATA.

### 5.5 USB 2.0

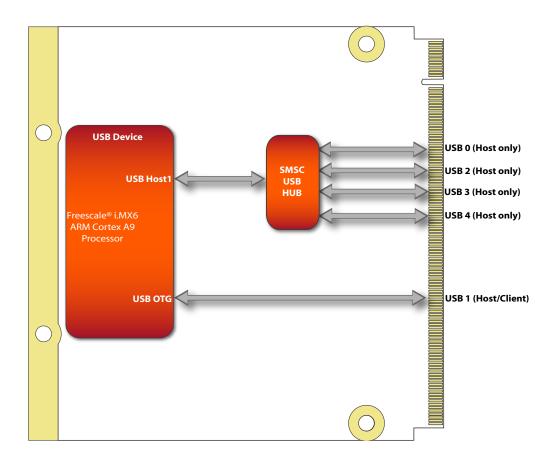

The conga-QMX6 offers five USB ports via USB 2.0 host controllers provided by the NXP® i.MX6 Cortex A9 processor. These controllers provide high performance USB functionality that complies with USB 2.0 specification and with OTG supplement.

The offered ports comprise of one USB OTG port and four USB hosts. These four USB hosts are derived through the integration of an SMSC USB hub, and are implemented by routing the USB H1 port of the processor to the SMSC Hub. The USB OTG port (OTG client) is connected directly to the USB\_OTG port of the i.MX6 processor.

The OTG client port can drop the hosting role and act as a normal USB device when conga-QMX6 is attached to another host. The direction of OTG port depends on the USB control signal (USB\_ID). If asserted high, the OTG is set to client and if low, the OTG port is set to host. All ports are capable of supporting USB 1.1 and 2.0 compliant devices.

#### 5.6 SD/SDIO/MMC

SDIO stands for Secure Digital Input Output. Devices that support SDIO can use small devices such as SD-Card or MMC-Card flash memories. The SD/SDIO/MMC cards communicate with the host system via the Ultra Secured Digital Host Controller (uSDHC). This controller acts as a bridge by sending commands and accessing data to and from the cards. The NXP® i.MX6 processor on the conga-QMX6 provides SD/SDIO/MMC controllers (SD1-SD4) for communicating with different SD, SDIO and MMC devices.

The conga-QMX6 offers one SDIO interface on the MXM connector via the NXP® i.MX6 SD4 port. Two other SDIO ports provided by the NXP® i.MX6 processor are supported onboard the conga-QMX6. These ports (SD2 and SD3) connect the onboard 4 bit micro SD and the onboard 8 bit eMMC respectively